Intel® Quartus® Prime Pro Edition User Guide: Platform Designer

A newer version of this document is available. Customers should click here to go to the newest version.

6.3. Tri-State Components

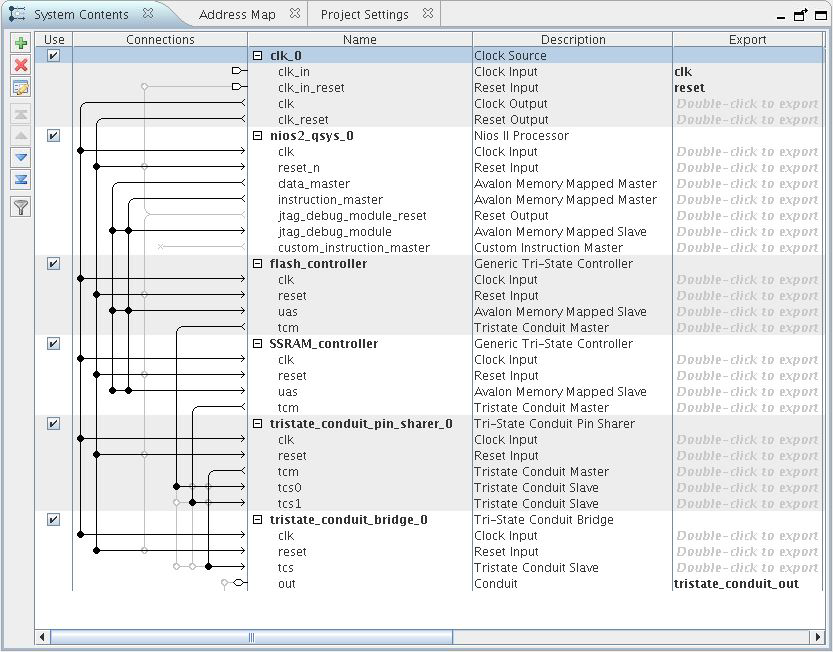

Tri-State Conduit System to Control Off-Chip SRAM and Flash Devices

In this example, there are two generic Tri-State Conduit Controllers. The first is customized to control a flash memory. The second is customized to control an off-chip SSRAM. The Tri-State Conduit Pin Sharer multiplexes between these two controllers, and the Tri-State Conduit Bridge converts between an on-chip encoding of tri-state signals and true bidirectional signals. By default, the Tri-State Conduit Pin Sharer and Tri-State Conduit Bridge present byte addresses. Typically, each address location contains more than one byte of data.

Address Connections from Platform Designer System to PCB

The flash device operates on 16‑bit words and must ignore the least‑significant bit of the Avalon memory mapped address. The figure shows addr[0]as not connected. The SSRAM memory operates on 32-bit words and must ignore the two low-order memory bits. Because neither device requires a byte address, addr[0] is not routed on the PCB.

The flash device responds to address range 0 MB to 8 MB-1. The SSRAM responds to address range 8 MB to 10 MB-1. The PCB schematic for the PCB connects addr[21:0] to addr[18:0] of the SSRAM device because the SSRAM responds to 32‑bit word address. The 8 MB flash device accesses 16‑bit words; consequently, the schematic does not connect addr[0]. The chipselect signals select between the two devices.