Visible to Intel only — GUID: box1719704927455

Ixiasoft

Visible to Intel only — GUID: box1719704927455

Ixiasoft

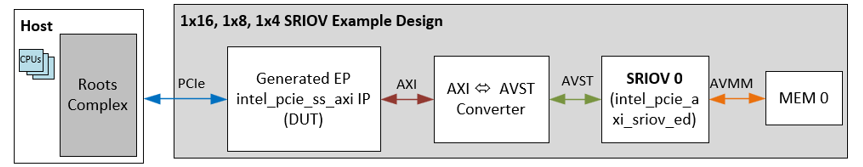

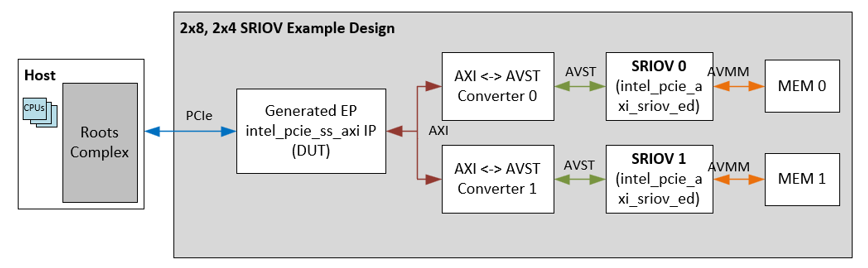

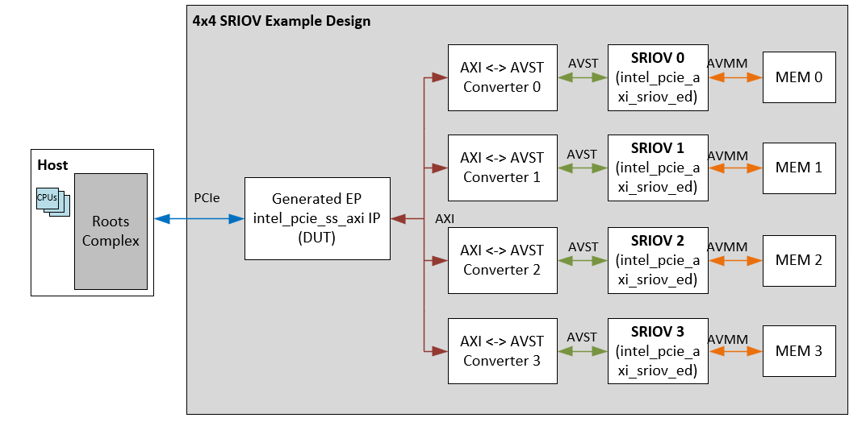

3.4.2. Functional Description for the Single Root I/O Virtualization (SR-IOV) Design Example

The SR-IOV design example performs memory transfers from a host processor to a target device. It supports up to two Physical Functions (PFs) and 32 Virtual Functions (VFs) per PF. Note that this design example does not support back-to-back transactions from the host processor since the design is intended to showcase single-dword transactions. In addition, the addresses for all the transactions must be dword-aligned.

This design example automatically creates the files necessary to simulate and compile in the Quartus® Prime software. You can download the compiled design to an Agilex™ 7 I-Series FPGA Development Kit.

| Port Mode | Link Width | Link Speed | HIP Data Width (Bits) | Application Data Width (Bits) | Compact/HIP Native Mode | Design Example Support |

|---|---|---|---|---|---|---|

| Endpoint | x16 | Gen4 | 512 (2 x 256) | 1024 (4 x 256) | Compact | SCTH |

| 512 (2 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| Gen3 | 512 (2 x 256) | 1024 (4 x 256) | Compact | SCTH | ||

| 512 (2 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| x8 | Gen4 | 256 (1 x 256) | 1024 (4 x 256) | Compact | SCTH | |

| 256 (1 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| Gen3 | 256 (1 x 256) | 1024 (4 x 256) | Compact | SCTH | ||

| 256 (1 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| x4 | Gen4 | 128 (1 x 128) | 256 (1 x 256) | Compact | CTH | |

| 128 (1 x 128) | 128 (1 x 128) | Compact | CTH | |||

| Gen3 | 128 (1 x 128) | 256 (1 x 256) | Compact | CTH | ||

| 128 (1 x 128) | 128 (1 x 128) | Compact | CTH | |||

| Root Port | N/A | N/A | N/A | N/A | N/A | N/A |

| TL Bypass | N/A | N/A | N/A | N/A | N/A | N/A |

| PIPE Direct (PIPE-D) | N/A | N/A | N/A | N/A | N/A | N/A |

| Port Mode | Link Width | Link Speed | HIP Data Width (Bits) | Application Data Width (Bits) | Compact/HIP Native Mode | Design Example Support |

|---|---|---|---|---|---|---|

| Endpoint | x16 | Gen4 | 512 (2 x 256) | 1024 (4 x 256) | Compact | SCTH |

| 512 (2 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| Gen3 | 512 (2 x 256) | 1024 (4 x 256) | Compact | SCTH | ||

| 512 (2 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| x8 | Gen4 | 256 (1 x 256) | 1024 (4 x 256) | Compact | SCTH | |

| 256 (1 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| Gen3 | 256 (1 x 256) | 1024 (4 x 256) | Compact | SCTH | ||

| 256 (1 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| x4 | Gen4 | 128 (1 x 128) | 256 (1 x 256) | Compact | CTH | |

| 128 (1 x 128) | 128 (1 x 128) | Compact | CTH | |||

| Gen3 | 128 (1 x 128) | 256 (1 x 256) | Compact | CTH | ||

| 128 (1 x 128) | 128 (1 x 128) | Compact | CTH | |||

| Root Port | N/A | N/A | N/A | N/A | N/A | |

| TL Bypass | N/A | N/A | N/A | N/A | N/A | |

| PIPE Direct (PIPE-D) | N/A | N/A | N/A | N/A | N/A |

| Port Mode | Link Width | Link Speed | HIP Data Width (Bits) | Application Data Width (Bits) | Compact/HIP Native Mode | Design Example Support |

|---|---|---|---|---|---|---|

| Endpoint | x16 | Gen5 | 1024 (4 x 256) | 1024 (4 x 256) | HIP Native | SCTH |

| 1024 (4 x 256) | 1024 (4 x 256) | Compact | SCTH | |||

| 1024 (4 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 1024 (4 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 1024 (4 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 1024 (4 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 1024 (4 x 256) | 256 ( 1 x 256) | Compact | SCTH | |||

| Gen4 | 1024 (4 x 256) | 1024 (4 x 256) | HIP Native | SCTH | ||

| 512 (2 x 256) | 1024 (4 x 256) | Compact | SCTH | |||

| 512 (2 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (2 x 256) | HIP Native | SCTH | |||

| 512 (2 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| Gen3 | 1024 (4 x 256) | 1024 (4 x 256) | HIP Native | SCTH | ||

| 512 (2 x 256) | 1024 (4 x 256) | Compact | SCTH | |||

| 512 (2 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (2 x 256) | HIP Native | SCTH | |||

| 512 (2 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| x8 | Gen5 | 512 (2 x 256) | 1024 (4 x 256) | Compact | SCTH | |

| 512 (2 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (2 x 256) | HIP Native | SCTH | |||

| 512 (2 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 512 (2 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 512 (2 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| Gen4 | 512 (2 x 256) | 512 (2 x 256) | HIP Native | SCTH | ||

| 256 (1 x 256) | 1024 (4 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 256 (1 x 256) | HIP Native | SCTH | |||

| 256 (1 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| Gen3 | 512 (2 x 256) | 512 (2 x 256) | HIP Native | SCTH | ||

| 256 (1 x 256) | 1024 (4 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 1024 (2 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 1024 (1 x 1024) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (2 x 256) | Compact | SCTH | |||

| 256 (1 x 256) | 512 (1 x 512) | Compact | SCTH | |||

| 256 (1 x 256) | 256 (1 x 256) | HIP Native | SCTH | |||

| 256 (1 x 256) | 256 (1 x 256) | Compact | SCTH | |||

| x4 | Gen5 | 256 (2 x 128) | 1024 (4 x 256) | Compact | CTH | |

| 256 (2 x 128) | 1024 (2 x 512) | Compact | CTH | |||

| 256 (2 x 128) | 1024 (1 x 1024) | Compact | CTH | |||

| 256 (2 x 128) | 512 (2 x 256) | Compact | CTH | |||

| 256 (2 x 128) | 512 (1 x 512) | Compact | CTH | |||

| 256 (2 x 128) | 256 (2 x 128) | HIP Native | CTH | |||

| 256 (2 x 128) | 256 (2 x 128) | Compact | CTH | |||

| 256 (2 x 128) | 256 (1 x 256) | Compact | CTH | |||

| Gen4 | 256 (2 x 128) | 256 (2 x 128) | HIP Native (4x4, 1x4) | CTH | ||

| 128 (1 x 128) | 256 (1 x 256) | Compact | CTH | |||

| 128 (1 x 128) | 128 (1 x 128) | HIP Native | CTH | |||

| 128 (1 x 128) | 128 (1 x 128) | Compact | CTH | |||

| Gen3 | 256 (2 x 128) | 256 (2 x 128) | HIP Native (4x4, 1x4) | CTH | ||

| 128 (1 x 128) | 256 (1 x 256) | Compact | CTH | |||

| 128 (1 x 128) | 128 (1 x 128) | HIP Native | CTH | |||

| 128 (1 x 128) | 128 (1 x 128) | Compact | CTH | |||

| Root Port | N/A | N/A | N/A | N/A | N/A | N/A |

| TL Bypass | N/A | N/A | N/A | N/A | N/A | N/A |

| PIPE Direct (PIPE-D) | N/A | N/A | N/A | N/A | N/A | N/A |