Intel® Arria® 10 Hard Processor System Technical Reference Manual

ID

683711

Date

1/10/2023

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. Intel® Arria® 10 Hard Processor System Technical Reference Manual Revision History

2. Introduction to the Hard Processor System

3. Clock Manager

4. Reset Manager

5. FPGA Manager

6. System Manager

7. SoC Security

8. System Interconnect

9. HPS-FPGA Bridges

10. Cortex*-A9 Microprocessor Unit Subsystem

11. CoreSight* Debug and Trace

12. Error Checking and Correction Controller

13. On-Chip Memory

14. NAND Flash Controller

15. SD/MMC Controller

16. Quad SPI Flash Controller

17. DMA Controller

18. Ethernet Media Access Controller

19. USB 2.0 OTG Controller

20. SPI Controller

21. I2C Controller

22. UART Controller

23. General-Purpose I/O Interface

24. Timer

25. Watchdog Timer

26. Hard Processor System I/O Pin Multiplexing

27. Introduction to the HPS Component

28. Instantiating the HPS Component

29. HPS Component Interfaces

30. Simulating the HPS Component

A. Booting and Configuration

10.3.1. Functional Description

10.3.2. Implementation Details

10.3.3. Cortex*-A9 Processor

10.3.4. Interactive Debugging Features

10.3.5. L1 Caches

10.3.6. Preload Engine

10.3.7. Floating Point Unit

10.3.8. NEON* Multimedia Processing Engine

10.3.9. Memory Management Unit

10.3.10. Performance Monitoring Unit

10.3.11. Arm* Cortex* -A9 MPCore* Timers

10.3.12. Generic Interrupt Controller

10.3.13. Global Timer

10.3.14. Snoop Control Unit

10.3.15. Accelerator Coherency Port

11.1. Features of CoreSight* Debug and Trace

11.2. Arm* CoreSight* Documentation

11.3. CoreSight Debug and Trace Block Diagram and System Integration

11.4. Functional Description of CoreSight Debug and Trace

11.5. CoreSight* Debug and Trace Programming Model

11.6. CoreSight Debug and Trace Address Map and Register Definitions

11.4.1. Debug Access Port

11.4.2. System Trace Macrocell

11.4.3. Trace Funnel

11.4.4. CoreSight Trace Memory Controller

11.4.5. AMBA* Trace Bus Replicator

11.4.6. Trace Port Interface Unit

11.4.7. Embedded Cross Trigger System

11.4.8. Program Trace Macrocell

11.4.9. HPS Debug APB* Interface

11.4.10. FPGA Interface

11.4.11. Debug Clocks

11.4.12. Debug Resets

14.1. NAND Flash Controller Features

14.2. NAND Flash Controller Block Diagram and System Integration

14.3. NAND Flash Controller Signal Descriptions

14.4. Functional Description of the NAND Flash Controller

14.5. NAND Flash Controller Programming Model

14.6. NAND Flash Controller Address Map and Register Definitions

15.1. Features of the SD/MMC Controller

15.2. SD/MMC Controller Block Diagram and System Integration

15.3. SD/MMC Controller Signal Description

15.4. Functional Description of the SD/MMC Controller

15.5. SD/MMC Controller Programming Model

15.6. SD/MMC Controller Address Map and Register Definitions

16.1. Features of the Quad SPI Flash Controller

16.2. Quad SPI Flash Controller Block Diagram and System Integration

16.3. Quad SPI Flash Controller Signal Description

16.4. Functional Description of the Quad SPI Flash Controller

16.5. Quad SPI Flash Controller Programming Model

16.6. Quad SPI Flash Controller Address Map and Register Definitions

16.4.1. Overview

16.4.2. Data Slave Interface

16.4.3. SPI Legacy Mode

16.4.4. Register Slave Interface

16.4.5. Local Memory Buffer

16.4.6. DMA Peripheral Request Controller

16.4.7. Arbitration between Direct/Indirect Access Controller and STIG

16.4.8. Configuring the Flash Device

16.4.9. XIP Mode

16.4.10. Write Protection

16.4.11. Data Slave Sequential Access Detection

16.4.12. Clocks

16.4.13. Resets

16.4.14. Interrupts

18.6.1. System Level EMAC Configuration Registers

18.6.2. EMAC FPGA Interface Initialization

18.6.3. EMAC HPS Interface Initialization

18.6.4. DMA Initialization

18.6.5. EMAC Initialization and Configuration

18.6.6. Performing Normal Receive and Transmit Operation

18.6.7. Stopping and Starting Transmission

18.6.8. Programming Guidelines for Energy Efficient Ethernet

18.6.9. Programming Guidelines for Flexible Pulse-Per-Second (PPS) Output

19.1. Features of the USB OTG Controller

19.2. USB OTG Controller Block Diagram and System Integration

19.3. USB 2.0 ULPI PHY Signal Description

19.4. Functional Description of the USB OTG Controller

19.5. USB OTG Controller Programming Model

19.6. USB 2.0 OTG Controller Address Map and Register Definitions

29.5.1.1. NAND Flash Controller Interface

29.5.1.2. SD/MMC Controller Interface

29.5.1.3. Quad SPI Flash Controller Interface

29.5.1.4. Ethernet Media Access Controller Interface

29.5.1.5. USB 2.0 OTG Controller Interface

29.5.1.6. SPI Controller Interface

29.5.1.7. I2C Controller Interface

29.5.1.8. UART Interface

30.1. Simulation Flows

30.2. Clock and Reset Interfaces

30.3. FPGA-to-HPS AXI Slave Interface

30.4. HPS-to-FPGA AXI Master Interface

30.5. Lightweight HPS-to-FPGA AXI Master Interface

30.6. HPS-to-FPGA MPU Event Interface

30.7. Interrupts Interface

30.8. HPS-to-FPGA Debug APB* Interface

30.9. FPGA-to-HPS System Trace Macrocell Hardware Event Interface

30.10. HPS-to-FPGA Cross-Trigger Interface

30.11. FPGA-to-HPS DMA Handshake Interface

30.12. Boot from FPGA Interface

30.13. Security Manager Anti-Tamper Signals Interface

30.14. EMIF Conduit

30.15. Pin MUX and Peripherals

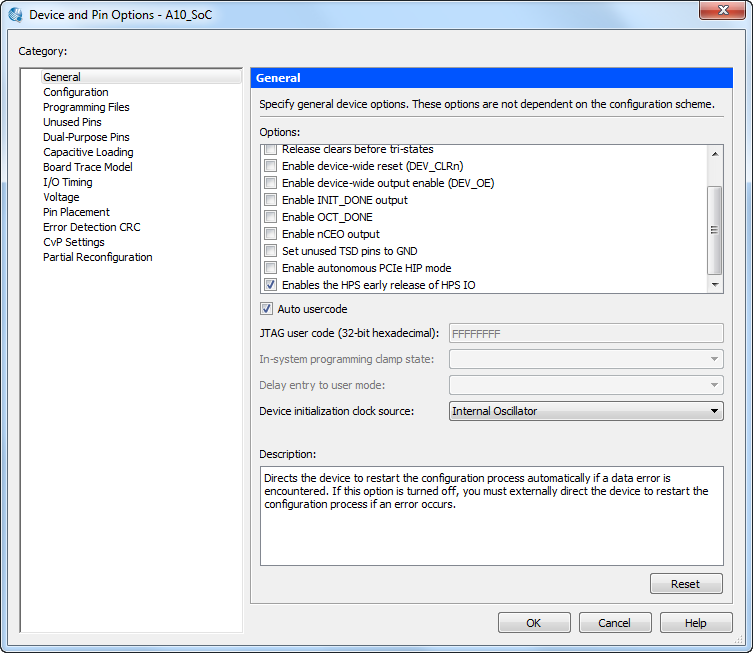

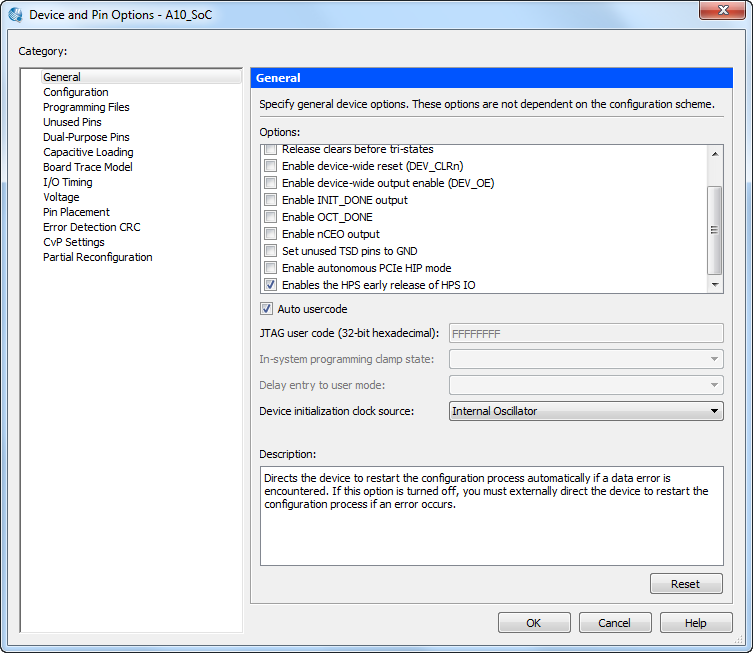

A.7.2. Early I/O Release FPGA Configuration Flow Through HPS

Figure 181. Early I/O Release FPGA Configuration Flow Through HPSThe I/Os are configured and the shared and hard memory controller I/Os are released so that the HPS has immediate access to them. The FPGA fabric configuration follows at a later time.

Note: The FPGA fabric is not required to be programmed immediately after the first I/O configuration. You can also program the I/Os, re-program the I/Os and then program the FPGA fabric as long as the early I/O release configuration option is enabled in each I/O configuration file.

Note: If you are using the early I/O release configuration flow, you cannot initially use SmartVID to power your device. Instead, you can use a fixed power supply until after the FPGA is configured. When the FPGA is configured, you can then enable SmartVID.

You can enable early I/O configuration in Intel® Quartus® Prime:

- Click on the the Assignments menu and select Device.

- When the Device settings window opens, click the Device and Pin Options button.

- In the General category, click on the option labeled "Enables the HPS early release of HPS IO".

Figure 182. Intel® Quartus® Prime Early I/O Release Setting