Visible to Intel only — GUID: lzg1715730966371

Ixiasoft

1. Overview

2. Install and License the GTS Ethernet Intel® FPGA Hard IP

3. Configure and Generate Ethernet Hard IP variant

4. Integrate GTS Ethernet Intel® FPGA Hard IP into Your Application

5. Simulate, Compile, and Validate (MAC+PCS) - Single Instance

6. Simulate, Compile, and Validate (MII PCS Only /PCS66 OTN/PCS66 FlexE) - Single Instance

7. Simulate, Compile, and Validate SyncE - Single Instance

8. Simulate and Compile PTP1588 - Single Instance

9. Simulate, Compile, and Validate - Multiple Instance

10. Simulate, Compile, and Validate - Auto-Negotiation and Link Training

11. Troubleshoot and Diagnose Issues

A. Appendix A: Functional Description

B. Appendix B: Configuration Registers

C. Appendix C: Document Revision History for the GTS Ethernet Intel® FPGA Hard IP User Guide

4.1. Implement Required Clocking

4.2. Implement Required Resets

4.3. Connect the Status Interface

4.4. Connect the MAC Avalon Streaming Client Interface

4.5. Connect the MII PCS Only Client Interface

4.6. Connect the PCS66 Client Interface – FlexE and OTN

4.7. Connect the Precision Time Protocol Interface

4.8. Connect the Ethernet Hard IP Reconfiguration Interface

4.9. Connect the Auto-Negotiation and Link Training

4.1.1. Implement MAC Synchronous Clock Connections to Single Instance

4.1.2. Implement MAC Synchronous Clock Connections to Multiple Instances

4.1.3. Implement Clock Connections to MAC Asynchronous Operation

4.1.4. Implement Clock Connections in Synchronous Ethernet Operation (Sync-E)

4.1.5. Implement Clock Connections in PTP-Based Design

4.4.1.1. Drive the Ethernet Packet to the TX MAC Avalon Streaming Client Interface with Disabled Preamble Passthrough

4.4.1.2. Drive the Ethernet Packet on the TX MAC Avalon Streaming Client Interface with Enabled Preamble Passthrough

4.4.1.3. Use i_tx_skip_crc to Control Source Address, PAD, and CRC Insertion

4.4.1.4. Assert the i_tx_error to Invalidate a Packet

4.4.2.1. Receive Ethernet Frame on the RX MAC Avalon Streaming Client Interface with Preamble Passthrough Disabled

4.4.2.2. Receive Ethernet Frame with Preamble Passthrough Enabled

4.4.2.3. Receive Ethernet Frame with Remove CRC bytes Disabled

4.4.2.4. Monitor Status and Errors on the RX MAC Avalon Streaming Client Interface

Visible to Intel only — GUID: lzg1715730966371

Ixiasoft

7.3.2. Simulator Output

The following sample output illustrates a successful simulation test run of the 10GE Ethernet with SyncE enabled in QuestaSim simulator. The script and waveform output is similar for other supported simulators.

---TX reset sequence completed ----- # The time now is 40000000000 # ---RX reset sequence completed ----- # The time now is 50000000000 # # ---IP_INST[ 0] Test 0; ---Total 16 packets to send----- # ------IP_INST[0] Start pkt gen TX----- # ------Checking Packet TX/RX result----- # ------2 packets Sent; 0 packets Received-------- # ---- 16 packets Sent; 16 packets Received-------- # ------ALL 16 packets Sent out--- # ------ALL 16 packets Received--- # ------TX/RX packet check OK--- # # ****Starting AVMM Read/Write**** # ====>MATCH! Read addr = 00000104, ReaddataValid = 1 Readdata = abcdef01 Expected_Readdata = abcdef01 # # The time now is 60000000000 # # ====>MATCH! Read addr = 00000108, ReaddataValid = 1 Readdata = 00000007 Expected_Readdata = 00000007 # # ====>MATCH! Read addr = 00100004, ReaddataValid = 1 Readdata = b1f05663 Expected_Readdata = b1f05663 # # ====>MATCH! Read addr = 00100008, ReaddataValid = 1 Readdata = 06b97b0d Expected_Readdata = 06b97b0d # # ====>MATCH! Read addr = 00100080, ReaddataValid = 1 Readdata = deadc0de Expected_Readdata = deadc0de # # ====>MATCH! Read addr = 00300080, ReaddataValid = 1 Readdata = deadc0de Expected_Readdata = deadc0de # # ====>MATCH! Read addr = 00000af0, ReaddataValid = 1 Readdata = 00000000 Expected_Readdata = 00000000 # # ====>MATCH! Read addr = 00050014, ReaddataValid = 1 Readdata = 22334455 Expected_Readdata = 22334455 # # ====>MATCH! Read addr = 0005001c, ReaddataValid = 1 Readdata = 000005ee Expected_Readdata = 000005ee # # ====>MATCH! Read addr = 00050014, ReaddataValid = 1 Readdata = 01234567 Expected_Readdata = 01234567 # # ====>MATCH! Read addr = 00050018, ReaddataValid = 1 Readdata = 000089ab Expected_Readdata = 000089ab # # ====>MATCH! Read addr = 000a5000, ReaddataValid = 1 Readdata = 00000000 Expected_Readdata = 00000000 # # **** AVMM Read/Write Operation Completed for IP_INST[ 0]**** # ** Testbench complete # ****************************************

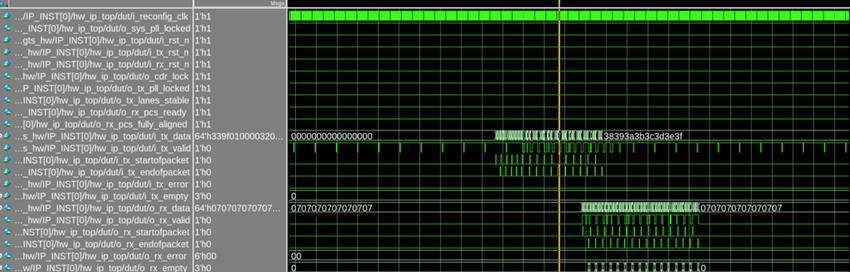

The following sample waveform illustrates a simulation test run of the 10GE Ethernet with SyncE enabled in QuestaSim simulator.