Visible to Intel only — GUID: fdr1693483558330

Ixiasoft

Visible to Intel only — GUID: fdr1693483558330

Ixiasoft

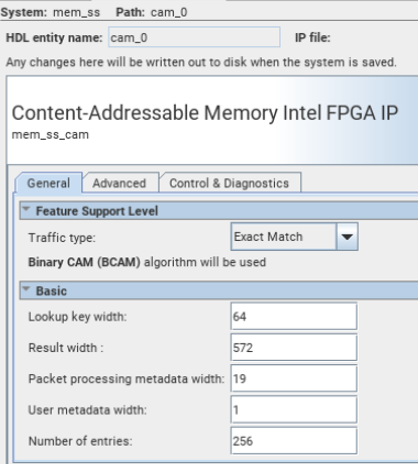

8.2.5.3. Parameterizing the Content-Addressable Memory (CAM) IP

M20K memory interface and associative storage result in a CAM IP with two types of traffic: Exact Match and Wildcard Match. Selecting Exact Match sets the CAM IP to use the BCAM algorithm, while selecting Wildcard Match results in the use of TCAM.

Using an external DDR4 memory interface along with the associative storage, produces a CAM IP with only the Exact Match traffic type enabled and the use of the MBL algorithm.

It is important to note that CAM IPs that use the M20K memory interface – and thus are BCAM or TCAM – export all their signals and conduits to the user logic. When using external DDR4 (CAM IP with MBL algorithm), the AXI Manager, AXI Clock, and Reset are all connected to the MSA.