Visible to Intel only — GUID: dxq1693483256224

Ixiasoft

Visible to Intel only — GUID: dxq1693483256224

Ixiasoft

8.2.1. Defining the Number of Memory Interfaces, Type, and Location

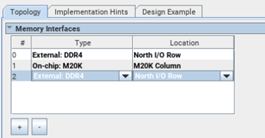

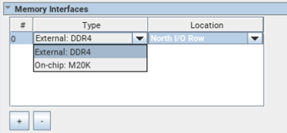

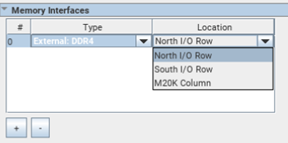

The following figures show the available high-level options for the memory interfaces that you will add to the memory subsystem IP. These define the type and physical location of the memory interfaces.

You can use external DDR4 type for storage purposes,or assign it to fabric or HPS, MBL CAM IP also relies on external memory. External DDR4 type can be used for storage purposes, assigned to fabric or HPS, MBL CAM IP also relies on external memory.

On-chip M20K memory is supported only to create BCAM and TCAM IPs. When you select this type of interface, you must select M20K Column on the Location list.

The following figure shows an example of three different memory interfaces; two are external DDR4 that can be used for fabric, HPS or MBL applications. An on-chip interface is also listed; this can be assigned only to a BCAM or TCAM interface.