Visible to Intel only — GUID: ems1502666107028

Ixiasoft

1.1. Acronyms and Definitions

1.2. Recommended System Requirements

1.3. Installation Folders

1.4. Boot Flow Overview

1.5. Getting Started

1.6. Enabling the UEFI DXE Phase and the UEFI Shell

1.7. Using the Network Feature Under the UEFI Shell

1.8. Creating your First UEFI Application

1.9. Using Arm* DS-5* Intel® SoC FPGA Edition (For Windows* Only)

1.10. Pit Stop Utility Guide

1.11. Porting HWLIBs to UEFI Guidelines

1.12. Tera Term Installation

1.13. Minicom Installation

1.14. Win32DiskImager Tool Installation

1.15. TFTPd64 By Ph.Jounin Installation

1.16. Revision History of Intel® Arria® 10 SoC UEFI Boot Loader User Guide

1.5.1. Compiling the Hardware Design

1.5.2. Generating the Boot Loader and Device Tree for UEFI Boot Loader

1.5.3. Building the UEFI Boot Loader

1.5.4. Creating an SD Card Image

1.5.5. Creating a QSPI Image

1.5.6. Booting the Board with SD/MMC

1.5.7. Booting the Board with QSPI

1.5.8. Early I/O Release

1.5.9. Booting Linux* Using the UEFI Boot Loader

1.5.10. Debugging an Example Project

1.5.11. UEFI Boot Loader Customization

1.5.12. Enabling Checksum for the FPGA Image

1.5.13. NAND Bad Block Management

Visible to Intel only — GUID: ems1502666107028

Ixiasoft

1.5.1.3. Compile the Design in Intel® Quartus® Prime

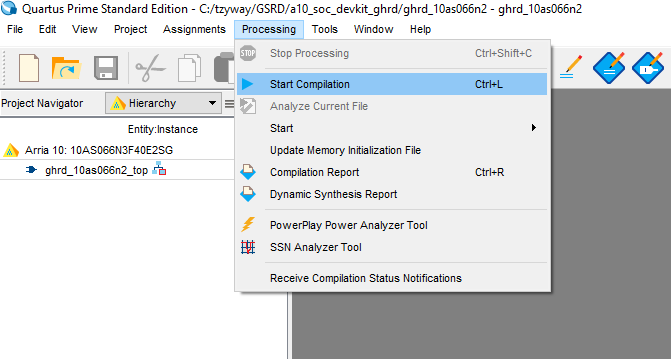

Compile the project in Intel® Quartus® Prime by selecting Processing > Start Compilation from the main menu.

Figure 11. Starting the Design Compilation

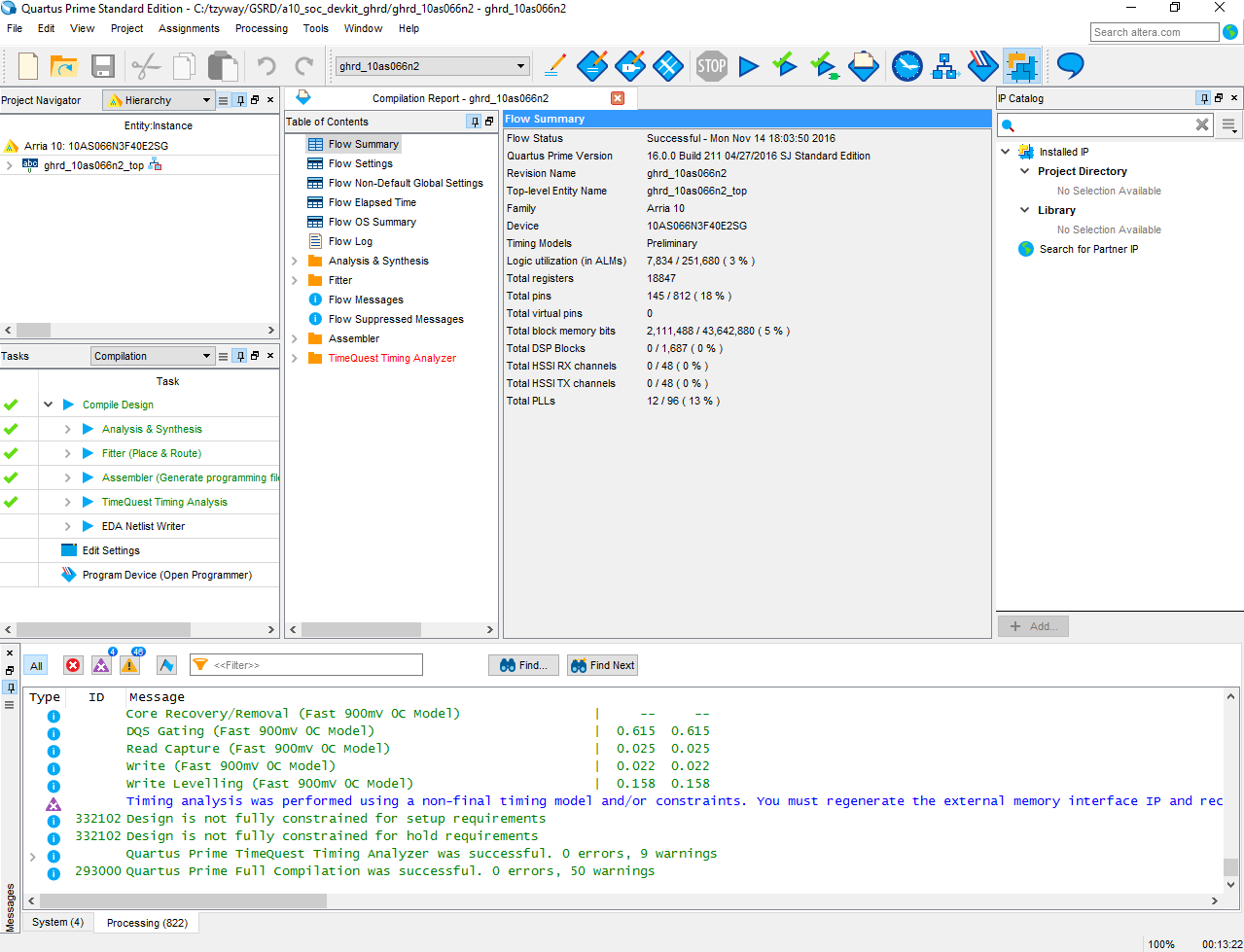

On completion, Intel® Quartus® Prime displays a compilation status in the Messages window below.

Figure 12. Compilation Messages and Status Window

The compilation process generates these files:

| File | Description |

|---|---|

| ~/a10_soc_devkit_ghrd/output_files/ghrd_10as066n2.sof | FPGA configuration file |

| ~/a10_soc_devkit_ghrd/hps_isw_handoff | Handoff folder containing XML files for generating the U-Boot device tree |