Visible to Intel only — GUID: sam1412661935327

Ixiasoft

ALTDQ_DQS2 Features

ALTDQ_DQS2 Device Support

Resource Utilization and Performance

ALTDQ_DQS2 Parameter Settings

ALTDQ_DQS2 Data Paths

ALTDQ_DQS2 Ports

Dynamic Reconfiguration for ALTDQ_DQS2

Stratix V Design Example

Arria V Design Example

IP-Generate Command

ALTDQ_DQS2 IP Core User Guide Archives

Document Revision History

I/O Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

DQS Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

I/O Configuration Block Bit Sequence for Arria V and Cyclone V Devices

DQS Configuration Block Bit Sequence for Arria V and Cyclone V Devices

Example Usage of Dynamic Reconfiguration for ALTDQ_DQS2

Visible to Intel only — GUID: sam1412661935327

Ixiasoft

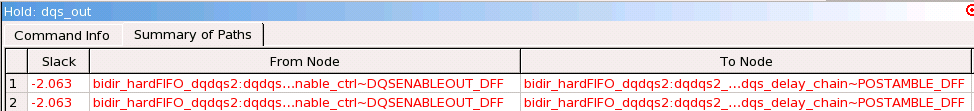

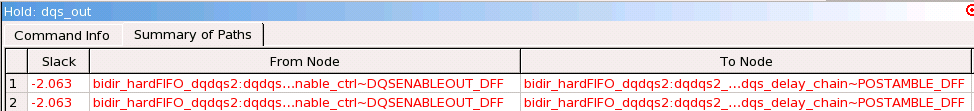

Timing Violation

The following figure shows a timing violation in the example design. This path is related to DQS enable control and is valid. Some calibration algorithm is required to control the DQS enable block.

Figure 45. Timing Violation

Without any calibration algorithm in place, this path cannot be set as false path in the static timing analysis.

set_false_path Command

#set_false_path -from [get_keepers {*|dqs_enable_ctrl~DQSENABLEOUT_DFF}] -to [get_clocks{dqs_out}]