Visible to Intel only — GUID: sam1412661879850

Ixiasoft

Visible to Intel only — GUID: sam1412661879850

Ixiasoft

DQS Write Operation

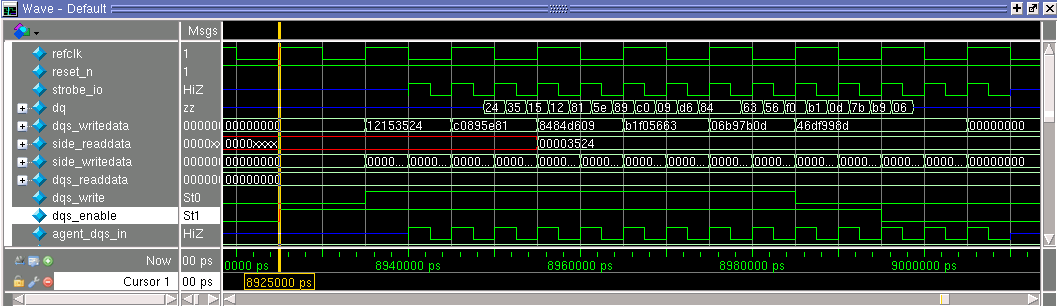

The driver asserting the dqs_enable signal at 8.925 ms begins the write operation. This will configure the ALTDQ_DQS2’s output_strobe_ena to high, getting ready to send out strobe to the DQS agent. The dqs_write signal is asserted at 8.935 ms. This sets the write_oe_in signal of the ALTDQ_DQS2 IP core to high, getting ready to send out data to the DQS agent. The data are written to the dqs_writedata of the DQS driver, and then reflected in the dq signal of the ALTDQ_DQS2 IP core. The data written out from the DQS driver is also stored in check_fifo. During the DQS write operation, the strobe_io and agent_dqs_in is toggling. Dqs_write deasserts at 8.985 ms and dqs_enable deasserts at 8.995ms. Outgoing data from the dq signal of the ALTDQ_DQS2 IP core is center-aligned to the strobe (strobe_io).

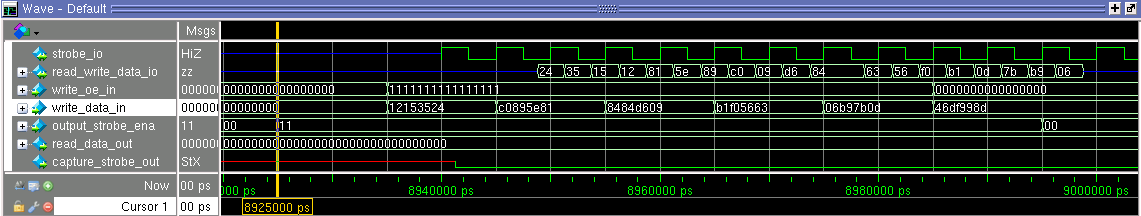

The following figure shows the DQS write operation waveform.

The following figure shows the waveform for the dynamic configuration simulation generated after executing topwave.do (located in the simulation/modelsim folder). The output_strobe_ena is held high from 8.925 ms to 8.995 ms while the strobe_io signal starts toggling only between 8.94 ms and 9.01 ms. The write_oe_in signal is held high throughout the five sets of valid write_data_in, which is between 8.935 ms and 8.955 ms. Center-aligned output data appears on the read_write_data_io signal between 8.949 ms and 8.999 ms.