Visible to Intel only — GUID: sam1412661870207

Ixiasoft

Visible to Intel only — GUID: sam1412661870207

Ixiasoft

Dynamic Configuration

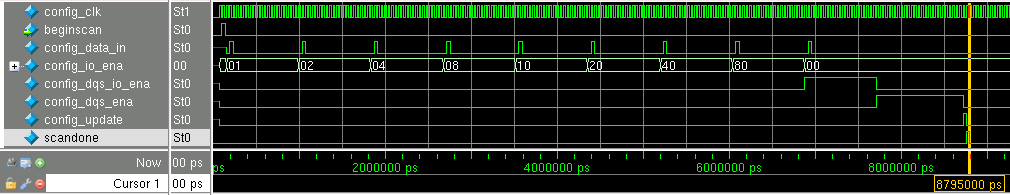

At 100 ns, there is a high pulse on the beginscan signal. When the agent_output_enable signal is pulled low, the strobe_io and agent_dqs_in goes to Hi-Z between 110 ns and 8.94 ms time mark, some internal calibration is being carried out. Dynamic configuration is the main feature used. At 8.795 ms time mark, the enable_driver signal is asserted. This specifies that the internal calibration is completed, and the control is passed on to the host controller (the DQS driver) to perform the normal read/write operation.

You can override the static values at runtime with a scan chain using the dynamic configuration feature in the ALTDQ_DQS2 IP core. To help you achieve static timing closure, the dynamic configuration feature allows you to override the static values at runtime with a scan chain. Each I/O and the DQS logic contain its own scan chain block (shift registers). This section shows you how to serially scan configuration bits into each scan chain block, between 100 ns and 8.795 ms time mark.

The following figure shows the waveform for the dynamic configuration simulation generated after executing topwave.do (located in the simulation/modelsim folder), between the high pulses of beginscan and scandone.

Because the enable_driver signal is asserted at 8.795 ms time mark, following read and write operations will be executed by DQS driver.

Section Content

DQS Write Operation

Side Read Operation

Side Write Operation

DQS Read Operation

Simulation Results

SDC Walkthrough