Visible to Intel only — GUID: sam1412661749580

Ixiasoft

Visible to Intel only — GUID: sam1412661749580

Ixiasoft

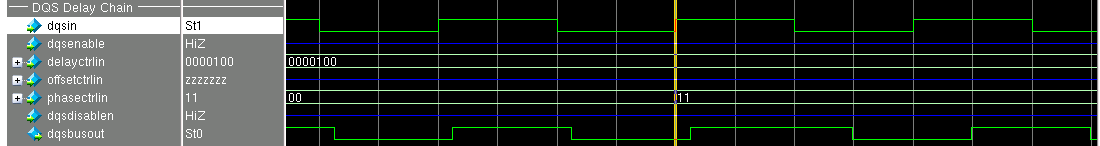

DQS Delay Chain

Because the DQS enable block is not applicable for this example design, the dqsenable signal is held at Hi-Z at all time. The dqsbusout signal is the delayed dqsin signal that drives to the dedicated DQS clock network to clock the DQ capture registers, so that data are captured at the center of the eye. If you disable the dynamic configuration feature, you should see a 67.5° phase shift (or 735 ps) between dqsin and dqsbusout, as expected due to the settings in Figure 1. The following figure shows that the phasectrlin signal is held at Hi-Z.

However, when you enable the dynamic configuration feature, phasectrlin (which is set via the dqsinputphasesetting port of the DQS configuration) determines the phase applied to the dqsbusout output.

Observe the following waveform. Before dynamic configuration, phasectrlin was set to 2'b00 and the shift between dqsin and dqsbusout is about 245 ps. Meanwhile after performing dynamic configuration, phasectrlin was set to 2'b11 and the shift between dqsin and dqsbusout is about 980 ps. The differences between 2'b11 (135°) and 2'b00 (0°) is 735 ps (67.5°). This is consistent with the settings in Figure 1 .