Visible to Intel only — GUID: sam1412661780447

Ixiasoft

Visible to Intel only — GUID: sam1412661780447

Ixiasoft

Dynamic Configuration

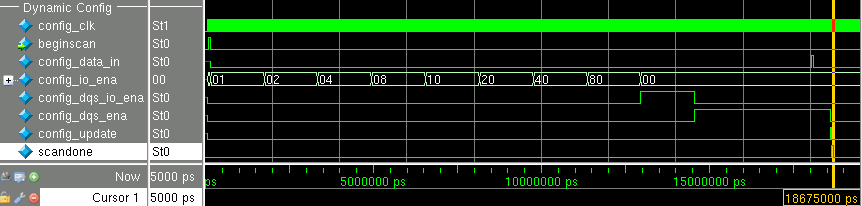

At 0.0001 ms, there is a high pulse on the beginscan signal. When the agent_output_enable signal is pulled low, some internal calibration is being carried out. Dynamic configuration is the main feature used. At 18.675 ms, the enable_driver signal is asserted to specify that the internal calibration is completed. The DQS driver, which acts as the host controller, performs a read/write operation.

To help you achieve static timing closure, the dynamic configuration feature allows you to override the static values at runtime with a scan chain. Each l/O and the DQS logic contains its own scan chain block (shift registers). This section shows you how to serially scan configuration bits into each scan chain block, between 0.0001 ms and 18.675 ms.

The following figure shows the waveform for the dynamic configuration simulation generated after executing topwave.do, in between the high pulses of beginscan and scandone. There is a pulse between 18.035 ms and 18.075 ms on the config_data_in signal. This is because the dqsinputphasesetting of the DQS configuration is set to 2'b01 in the testbench.

Because the enable_driver signal is asserted at 18.675 ms, the DQS driver performs the following operations:

Section Content

DQS Write Operation

Side Read Operation

Side Write Operation

DQS Read Operation

Simulation Results