6.2.1.1.7. Selecting a Processor Instance in a Multiple Processor Design

In a design with multiple Nios® II processors, you must create a different software project for each processor. When you create an application project, the Nios® II Software Build Tools for Eclipse require that you specify a Board Support Package (BSP) project. If a BSP for your application project does not yet exist, you can create one. For BSP generation, you must specify the CPU to which the application project is targeted.

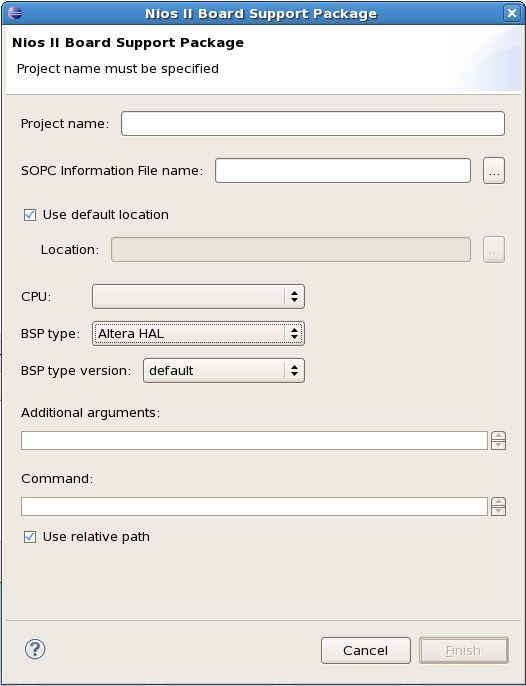

The figure below shows how you specify the CPU for the BSP in the Nios® II Software Build Tools for Eclipse. The Nios® II Board Support Package page of the New Project wizard collects the information required for BSP creation. This page derives the list of available CPU choices from the .sopcinfo file for the system.

From the Nios® II Command Shell, the jtagconfig –n command identifies available JTAG devices and the number of CPUs in the subsystem connected to each JTAG device. The example below shows the system response to a jtagconfig -n command.

Two-FPGA System Response to jtagconfig Command

[Platform Designer]$ jtagconfig -n 1) Intel® FPGA Download Cable [USB-0] 120930DD EP2S60 Node 19104600 Node 0C006E00 2) Intel® FPGA Download Cable [USB-1] 020B40DD EP2C35 Node 19104601 Node 19104602 Node 19104600 Node 0C006E00

The response in the example lists two different FPGAs, connected to the running JTAG server through different Intel® FPGA Download Cable cables. The cable attached to the USB-0 port is connected to a JTAG node in a Platform Designer subsystem with a single Nios® II core. The cable attached to the USB-1 port is connected to a JTAG node in a Platform Designer subsystem with three Nios® II cores. The node numbers represent JTAG nodes inside the FPGA. The appearance of the node number 0x191046xx in the response confirms that your FPGA implementation has a Nios® II processor with a JTAG debug module. The appearance of a node number 0x0C006Exx in the response confirms that the FPGA implementation has a JTAG UART component. The CPU instances are identified by the least significant byte of the nodes beginning with 191. The JTAG UART instances are identified by the least significant byte of the nodes beginning with 0C. Instance IDs begin with 0.

Only the CPUs that have JTAG debug modules appear in the listing. Use this listing to confirm you have created JTAG debug modules for the Nios® II processors you intended.