4.3.3.2. Example Hardware

The simple hardware designs, emphasizing MPU usage, are easily portable to other hardware platforms. There are two design examples, both targeting the NEEK. In one, the MPU specifies region sizes by mask, and in the other the MPU specifies region sizes by limit. Aside from this detail of MPU instantiation, the two designs are identical.

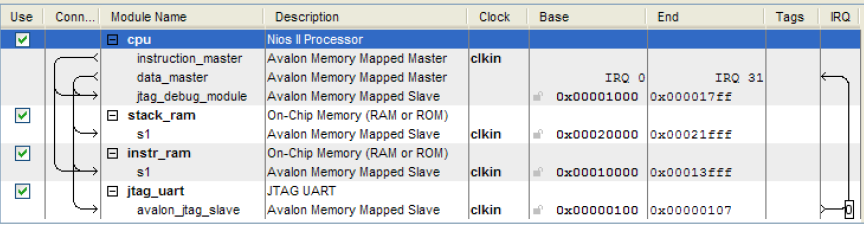

The address map is designed to make MPU configuration very straightforward. For instance, the instr_ram and stack_ram memories reside on valid region boundaries, and the JTAG UART base address is unique and aligned to a valid region boundary, as illustrated in Figure 40.

The figure below illustrates one of the design examples as it appears in Platform Designer. The hardware addresses fall on valid MPU region boundaries. While this constraint is not required, it is more convenient for the software engineer.