3.3.3. PCI Express* Interface

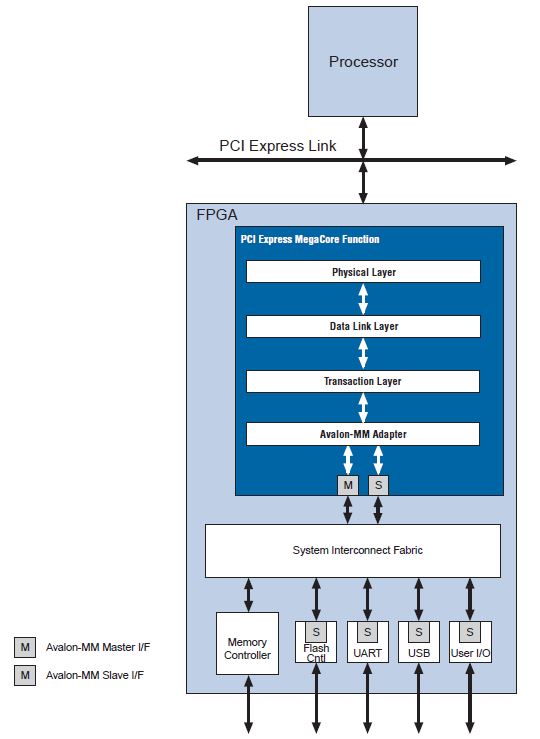

The Intel IP Compiler for PCI Express* configured using the Platform Designer design flow uses the IP Compiler for PCI Express* 's Avalon-MM bridge module to connect the IP Compiler for PCI Express* component to the system interconnect fabric. The bridge facilitates the design of PCI Express* systems that use the Avalon-MM interface to access Platform Designer components. The figure below illustrates a design that links an external processor to an Platform Designer system using the IP Compiler for PCI Express* .

You can also implement the IP Compiler for PCI Express* using the Parameter Editor design flow. The configuration options for the two design flows are different. The IP Compiler for PCI Express* is available in Intel FPGA devices as a hard IP implementation and can be used as a root port or end point. I

The figure shows an example system in which an external processor communicates with an Intel FPGA through a PCI Express* link.

For more information about using the IP Compiler for PCI Express* refer to the following reference documents: