3.3.2. RapidIO Interface

RapidIO is a high-performance packet-switched protocol that transports data and control information between processors, memories, and peripheral devices. The RapidIO Intel® FPGA IP function is available in Platform Designer includes Avalon® -MM ports that translate Serial RapidIO transactions into Avalon® -MM transactions. The Intel® FPGA IP function also includes an optional Avalon® Streaming ( Avalon® -ST) interface that you can use to send transactions directly from the transport layer to the system interconnect fabric. When you select all optional features, the core includes the following ports:

- Avalon® -MM I/O write master

- Avalon® -MM I/O read master

- Avalon® -MM I/O write slave

- Avalon® -MM I/O read slave

- Avalon® -MM maintenance master

- Avalon® -MM system maintenance slave

- Avalon® Streaming sink pass-through TX

- Avalon® -ST source pass-through RX

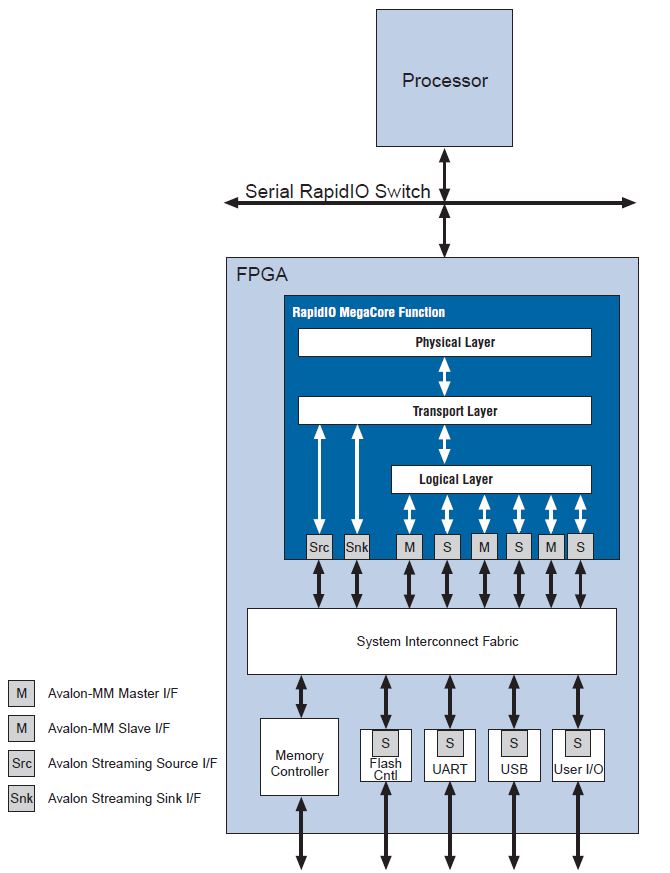

Using the Platform Designer design flow, you can integrate a RapidIO endpoint in a Platform Designer system. You connect the ports using the Platform Designer System Contents tab and Platform Designer automatically generates the system interconnect fabric. The figure below illustrates a Platform Designer system that includes a processor and a RapidIO Intel® FPGA IP function.

Refer to the RapidIO trade association web site's product list at rapidio.org for a list of processors that support a RapidIO interface.

Refer to the following documents for a complete description of the RapidIO Intel® FPGA IP function: RapidIO Intel® FPGA IP Function User Guide and AN513: RapidIO Interoperability With TI 6482 DSP Reference Design.