Visible to Intel only — GUID: iga1447447390570

Ixiasoft

Visible to Intel only — GUID: iga1447447390570

Ixiasoft

6.2.2.5. Breakpoints

You can set hardware breakpoints on code located in read-only memory such as flash memory. If you set a breakpoint in a read-only area of memory, a hardware breakpoint, rather than a software breakpoint, is selected automatically.

To enable hardware breakpoints, you must configure the Nios® II processor’s debug level in Platform Designer to debug level 2 or higher. To configure the Nios® II processor’s debug level in Platform Designer to the appropriate level, perform the following steps:

- On the Platform Designer System Contents tab, right-click the desired Nios® II processor component.

- On the right button pop-up menu, click Edit. The Nios® II processor configuration page appears.

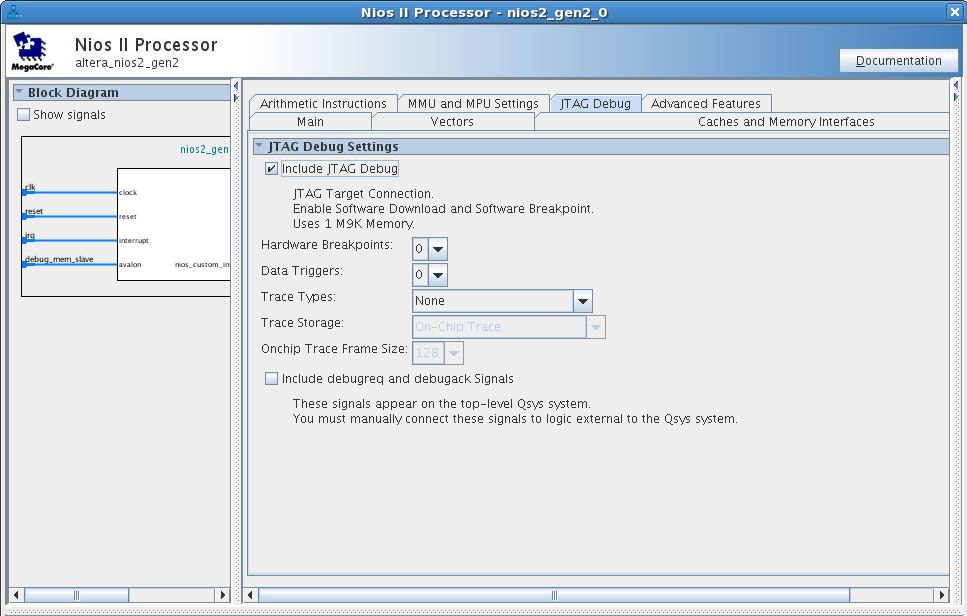

- Click the JTAG Debug Module tab, shown in the figure below.

- Select Level 2, Level 3, or Level 4.

- Click Finish.

Depending on the debug level you select, a maximum of four hardware breakpoints are available. The figure below shows the number of hardware breakpoints available for each debug level. The higher your debug level, the more logic resources you use on the FPGA.

For more information about the Nios® II processor debug levels, refer to the Instantiating the Nios® II Processor chapter in the Nios® II Gen2 Processor Reference Handbook.