PCB Design Guidelines (HSSI, EMIF, MIPI, True Differential, PDN) User Guide: Agilex™ 5 FPGAs and SoCs

Visible to Intel only — GUID: uzr1724038890848

Ixiasoft

Visible to Intel only — GUID: uzr1724038890848

Ixiasoft

5.4.1. VREF_CA/RESET Signal Routing Guidelines for Memory Down Topologies

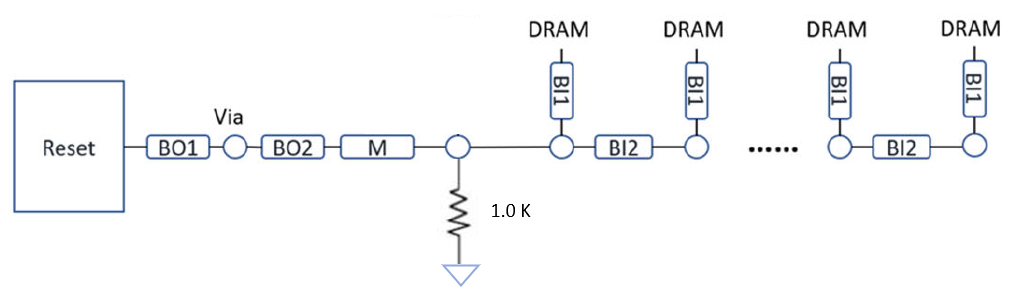

The following figure shows the reset routing scheme and setting, which you can apply to both single rank and dual-rank memory down topologies.

The target impedance for the reset signal is 50 ohms. The reset signal shall have at least 3 x h (where h represents trace to nearest reference plane height or distance) spacing to other nearby signals on the same layer. The end-to-end reset trace length is not limited but shall not exceed more than 5 inches to the first DRAM. Altera recommends using 1.0K ohm pull-down resistor for reset termination.

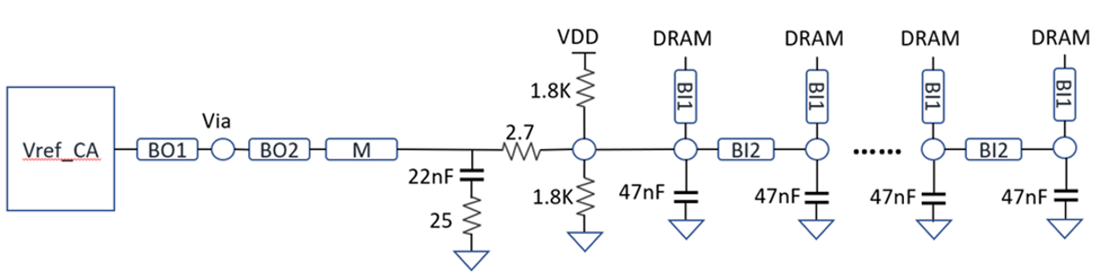

The following figure shows a VREF_CA routing scheme and setting, which you can apply to both single rank and dual-rank memory down topologies.

Altera recommends that you use at least a 10 mil trace width for VREF_CA routing on the PCB. The VREF_CA signal should have at least 3 × h (where h represents trace to nearest reference plane height or distance) spacing to other nearby signals on the same layer. The 1.8K ohm voltage divider circuitry shall be replaced by a 0.9K ohm resistor, pulled up to 0.6 V from the voltage regulator.