Visible to Intel only — GUID: zrg1724038371089

Ixiasoft

Visible to Intel only — GUID: zrg1724038371089

Ixiasoft

5.4. DDR4 Routing Guidelines

Single Rank x 8 Memory Down Topology

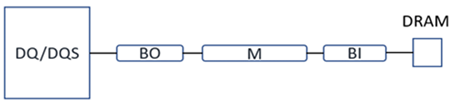

The single rank x 8 discrete interface covers data bytes (DQ/DQS), address signals, command signals (BA, BG, RAS, CAS, WE, ACT, PAR), control signals (CKE, CS, ODT) and CLKs.

The following figure illustrate the single rank x 8 memory down topology stripline routing for the BGA inner pins design example.

The following figures illustrate the single rank x 8 memory down topology for microstrip routing on the outer layer for BGA edge pins.

The following tables show the stripline routing for BGA inner pins and microstrip routing for BGA outer pins with the single rank x 8 memory down topology.

|

|

|

|

Single Rank x 16 Memory Down Topology

A single channel with single rank and x 16 memory devices, this interface covers data bytes (DQ/DQS), address signals, command signals (BA, BG, RAS, CAS, WE, ACT, PAR), control signals (CKE, CS, ODT) and clocks (CLK).

The following figures illustrate the single rank x 16 memory down topology of stripline routing for BGA inner pins. You can adjust the design topology based on the actual PCB design (single rank x 16 or dual-rank x 16).

The following figures illustrate the design example of single rank x 16 memory down topology microstrip routing for BGA outer pins. You can adjust the design based on the actual PCB design (single rank or dual-rank).

The following tables shows the stripline routing guideline for BGA inner pins and microstrip routing for BGA outer pins with single rank memory down topology.

|

|

|

|