PCB Design Guidelines (HSSI, EMIF, MIPI, True Differential, PDN) User Guide: Agilex™ 5 FPGAs and SoCs

Visible to Intel only — GUID: sfs1723801123679

Ixiasoft

Visible to Intel only — GUID: sfs1723801123679

Ixiasoft

5.2. LPDDR5 Interface Design Guidelines

LPDDR5/Memory Down Topology (Single Rank or Dual-Rank)

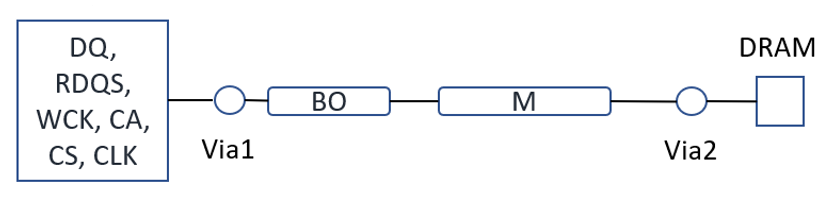

LPDDR5 memory down support is available in two configurations: single rank or dual-rank. There are four DRAM interface signal groupings: Data Group, Command-Address Group, Control Group, and Clock Group. The FPGA to DRAM connection uses point-to-point topology for data group, command-address group, control group, and clock group. The following figure shows the stripline routing topology for FPGA inner pins.

The following figure illustrates the Reset signal routing topology, recommend using 1.0K ohm pull-down resistor for Reset signal termination.

The LPDDR5 interface does not support a traditional dual-directional data-strobe architecture. However, two single-directional data strobes such as Write Clock (WCK) for Write Operations and an optional Read Clock (RDQS) for Read Operations are supported.

The following two figures show the T-line connection topology for WCK signal.

The following figure shows the daisy or T-Line connection topology for CA, CLK, and CTRL signals.

|

|

|

|

Reset signal routing design also follows the CMD/ADD/CTRL routing design. Maintain at least 3x h of space between the Reset signal to other signals (edge to edge) on the same layer.

Skew matching for LPDDR5 interface consists of both package routing skew and PCB physical routing skew. Use 3 time of dielectric height (h) for serpentine routing spacing. Skew matching of CA and CTRL with respect to the clock signals must be maintained to ensure signals at receiver are correctly sampled. In addition, there are skew matching requirements for DQ and DQS within a byte group, DQS and CLK.

The following table provides a detailed skew matching guideline.

|

|

The LPDDR5 eye margin is sensitive to the crosstalk, especially when signals are routed on deep layers; note that the deep-layer vertical transition induces greater vertical coupling and more crosstalk between signals. You can run simulations to determine the routing layer and whether to use backdrilling.