Visible to Intel only — GUID: rvy1692299602064

Ixiasoft

Visible to Intel only — GUID: rvy1692299602064

Ixiasoft

3.1.3.1. Lockstep Configuration

The primary controller drives the address and command bus and 32-bits of the DQ bus, while the other controllers drive the remainder of the DQ bus.

The following table summarizes the supported lockstep configurations:

| Memory Protocol | Configuration | DQ Width | AXI Interface |

|---|---|---|---|

| DDR4 | x40 | 40 | 256 b + 64 b USER DATA |

| DDR4 | x64 | 64 | 512 b |

| DDR4 | x64 with ECC 1 | 72 | 512 b |

| DDR4 | x72 | 72 | 512 b + 64 b USER DATA |

To ensure that the controllers remain coordinated in lockstep, the following points apply:

- Lockstep configurations support only synchronous fabric clocking mode. NoC Mode is not supported.

- Some of the controller scheduling and optimization features are disabled.

- There are limitations on the types of AXI transactions supported. Refer to the following table for details.

Table 4. Limitations for Lockstep Configuration in ES Devices Memory Protocol Configuration Limitation DDR4 x72 Supports AXI transfer size= 6 only. DDR4 x64 AXI transfer size min = 1* (2 bytes). DDR4 x64 Supports 2-byte aligned transfers only. DDR4 x40 Supports AXI transfer size= 5 only. DDR4 x40 Support 32-bit aligned transfers only.

Two Controllers in Lockstep Within One IO96 Bank

The EMIF IP instantiates 2 controllers within one IO96 bank to support x40 configurations. The AXI bus is configured as 256-bits wide plus 64-bits of user data (WUSER/RUSER), to generate the required 320-bits of data to transfer a burst-of-8 of 40-bit DQ. The following table illustrates how the AXI WDATA/RDATA and WUSER/RUSER can be mapped to the DQ lanes.

| Transfer | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|---|

| WDATA/RDATA | 31:0 | 63:32 | 95:64 | 127:96 | 159:128 | 191:160 | 223:192 | 255:224 |

| DQ | [31:0] | |||||||

| WUSER/RUSER | 7:0 | 15:8 | 23:16 | 31:24 | 39:32 | 47:40 | 55:48 | 63:56 |

| DQ | [39:32] | |||||||

This configuration can support only 3 address/command lane configurations, because there are only 8 byte lanes in one IO96 bank. The WUSER/RUSER signal is mapped to byte lane 7 (DQ lane with prefix s) in x40 configuration.

| Scheme | BL0 | BL1 | BL2 | BL3 | BL4 | BL5 | BL6 | BL7 |

|---|---|---|---|---|---|---|---|---|

| DDR4_AC_TOP | DQ[4] | DQ[3] | DQ[2] | DQ[1] | AC1 | AC2 | AC0 | sDQ[0] |

| DDR4_AC_BOT | DQ[0] | AC0 | AC1 | AC2 | DQ[1] | DQ[2] | DQ[3] | sDQ[4] |

Two/Three Controllers in Lockstep Within One IO96 Bank

This configuration is supported only in DDR4. The EMIF IP instantiates two or three controllers across two adjacent IO96 banks for the configurations listed in the table below.

| Configuration | DQ Width | AXI Interface | Notes |

|---|---|---|---|

| x64 | 64 | 512b | 2 controllers used. |

| x64 with ECC | 72 | 512b | 3 controllers used. ECC will be generated and checked by a soft IP block within the EMIF IP. |

| x72 | 72 | 512b + 64b USER DATA | 3 controllers used. |

For the x72 configuration, the AXI bus is configured as 512-bits wide, plus 64-bits of user data (WUSER/RUSER). The following example illustrates how you can map the AXI WDATA/RDATA and WUSER/RUSER to the DQ lanes. In this illustration, the WUSER/RUSER is mapped to the byte lane used for DQ [71:64].

The actual DQ lane to which the WUSER/RUSER is mapped depends on the address and command placement used. In each supported address and command placement scheme, the WUSER/RUSER is mapped to the DQ lane that has a prefix s (for example, sDQ0, sDQ4 or sDQ8). Refer to the following tables in the DDR4 Data Width Mapping topic, to identify the actual DQ lane used for WUSER/RUSER:

- Supported Lockstep configuration for DDR4 x64

- Supported Lockstep configuration for DDR4 x72 or x64 (with ECC)

| Transfer | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|---|---|---|---|---|---|---|---|---|

| WDATA/RDATA | 63:0 | 127:64 | 191:128 | 255:192 | 319:256 | 383:320 | 447:384 | 511:448 |

| DQ | [63:0] | |||||||

| WUSER/RUSER | 7:0 | 15:8 | 23:16 | 31:24 | 39:32 | 47:40 | 55:48 | 63:56 |

| DQ | [71:64] | |||||||

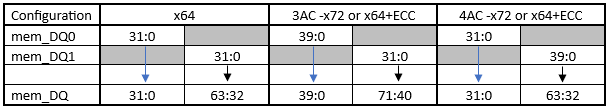

The generated IP has 2 mem DQ ports, collectively labeled as mem_DQ0 and mem_DQ1. The mapping below shows how these 2 ports are grouped into one single wide DQ port: