Visible to Intel only — GUID: ukk1659556061404

Ixiasoft

Visible to Intel only — GUID: ukk1659556061404

Ixiasoft

6.3.3. Reference Stackup

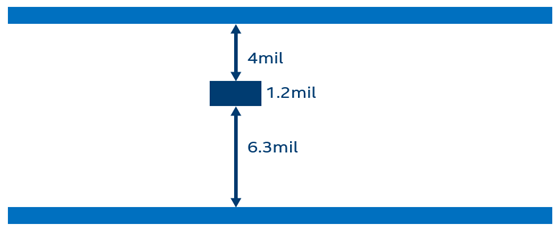

It is important to understand that trace geometry such as width, thickness, and edge-to-edge spacing, and the distance to reference planes, all impact trace impedance and crosstalk levels.

| Layer | Type | Thickness |

|---|---|---|

| SM TOP | 0.5 | |

| L1 | signal | 1.8 |

| D1 | prepreg | 2.7 |

| L2 | gnd/power | 1.2 |

| D2 | core | 4.0 |

| L3 | signal | 1.2 |

| D3 | prepreg | 6.3 |

| L4 | gnd/power | 1.2 |

| D4 | core | 4.0 |

| L5 | signal | 1.2 |

| D5 | prepreg | 6.3 |

| L6 | gnd/power | 1.2 |

| D6 | core | 4.0 |

| L7 | signal | 1.2 |

| D7 | prepreg | 6.3 |

| L8 | gnd | 1.2 |

| D8 | core | 4 |

| Power | 1.2 | |

| prepreg | 6.3 | |

| power | 1.2 | |

| core | 4 | |

| gnd | 1.2 | |

| prepreg | 6.3 | |

| power | 1.2 | |

| core | 4 | |

| L9 | gnd | 1.2 |

| D9 | prepreg | 6.3 |

| L10 | signal | 1.2 |

| D10 | core | 4.0 |

| L11 | gnd/power | 1.2 |

| D11 | prepreg | 6.3 |

| L12 | signal | 1.2 |

| D12 | core | 4.0 |

| L13 | gnd/power | 1.2 |

| D13 | prepreg | 6.3 |

| L14 | signal | 1.2 |

| D14 | core | 4.0 |

| L15 | gnd/power | 1.2 |

| D15 | prepreg | 2.7 |

| L16 | signal | 1.8 |

| SM BOT | 0.5 | |

| Total | 120.1 |

The reference stackup height is selected to be 120 mil to cover maximum signal via coupling (110mil) in simulation while extracting EMIF design guideline. Intel® recommends that board designers do not exceed 110mil signal via coupling (stripline routing on inner layers) in the EMIF layout PCB design for DDR4 interfaces.

If the PCB stackup exceeds 120 mil in height, Intel® recommends routing EMIF signals on upper layers, not to exceed more than 110 mil of signal via coupling.

The reference stackup materials in the above figure are selected as FR4, to represent worst-case signal loss in design phase simulation. In case of low-loss materials, the maximum end-to-end routing length shall be larger than the recommended end-to-end routing length in the design guidelines; however, you must perform time-domain channel simulation to ensure that timing requirements are met.