Visible to Intel only — GUID: xez1693102211275

Ixiasoft

Visible to Intel only — GUID: xez1693102211275

Ixiasoft

7.3.1. PCB Stack-up and Design Considerations

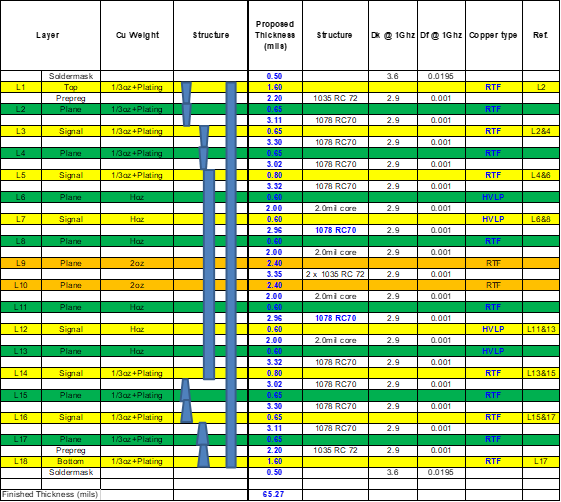

The following figure shows an example of an 18-layer PCB stackup that has been used for DDR5 on an Intel platform board. You may use other stackups (thin such as PCIE board, or thick board), provided you follow the recommendations in these guidelines.

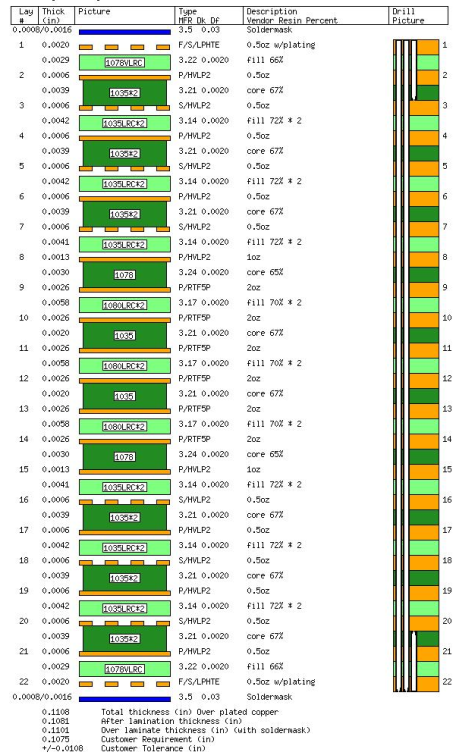

The following figure shows an example of a 22-layer thick PCB stackup, as used with some Intel platform boards and development kits.

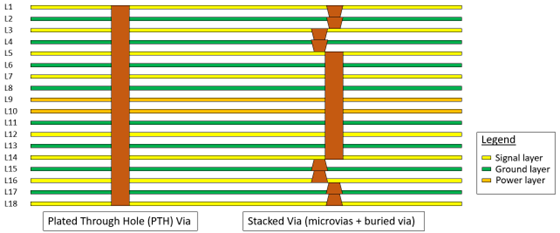

A high-quality type-4 PCB uses not only plated-through-hole (PTH) vias to connect from the top to bottom layer, but also stacked vias, micro vias, and buried vias to connect between layers. For example, a full-height stacked via of an 18 layer PCB consists of a combination of dual-stacked micro vias and buried vias. The following figure shows a cross-sectional comparison of a PTH and stacked via.

To support maximum data rate operation, DDR5 board design requires a high-quality PCB stackup using micro vias, buried vias, or stacked vias to reduce crosstalk for high performance. Reducing the length of signal via is essential to minimizing the crosstalk between signals.

A type-3 PCB with zero-built up layers and PTH vias which is used to implement a DDR4 design can also be used for DDR5 designs.