Visible to Intel only — GUID: mnz1474306594800

Ixiasoft

Visible to Intel only — GUID: mnz1474306594800

Ixiasoft

7.4.9.2. Equations for QDR-IV Board Skew Parameters

| Parameter | Description/Equation |

|---|---|

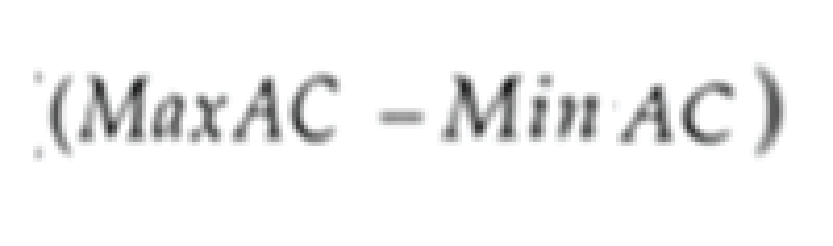

| Maximum system skew within address/command bus | The largest skew between the address and command signals. Enter combined board and package skew.

|

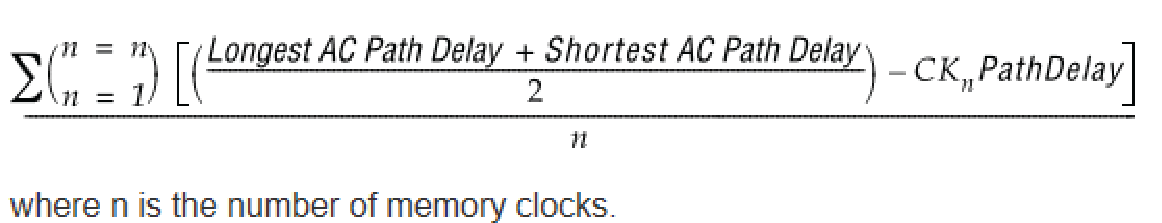

| Average delay difference between address/command and CK | The average delay difference between the address and command signals and the CK signal, calculated by averaging the longest and smallest Address/Command signal delay minus the CK delay. Positive values represent address and command signals that are longer than CK signals and negative values represent address and command signals that are shorter than CK signals. The Quartus Prime software uses this skew to optimize the delay of the address and command signals to have appropriate setup and hold margins.

|

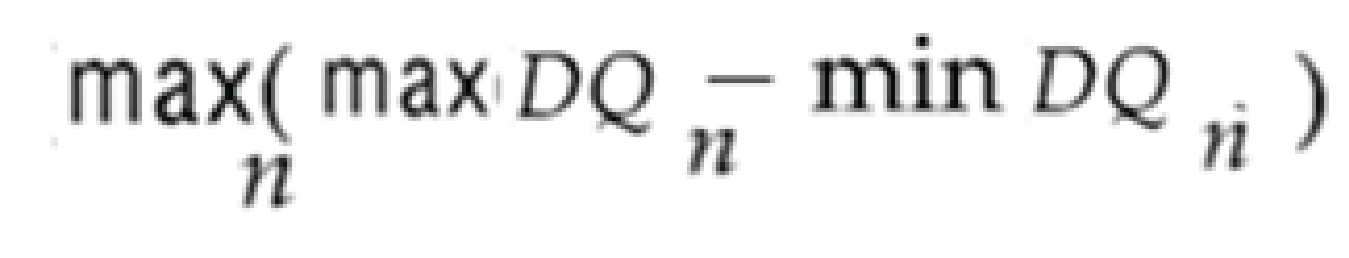

| Maximum System skew within QK group | The largest skew between all DQ and DM pins in a QK group. Enter combined board and package skew. This value affects the read capture and write margins.

|

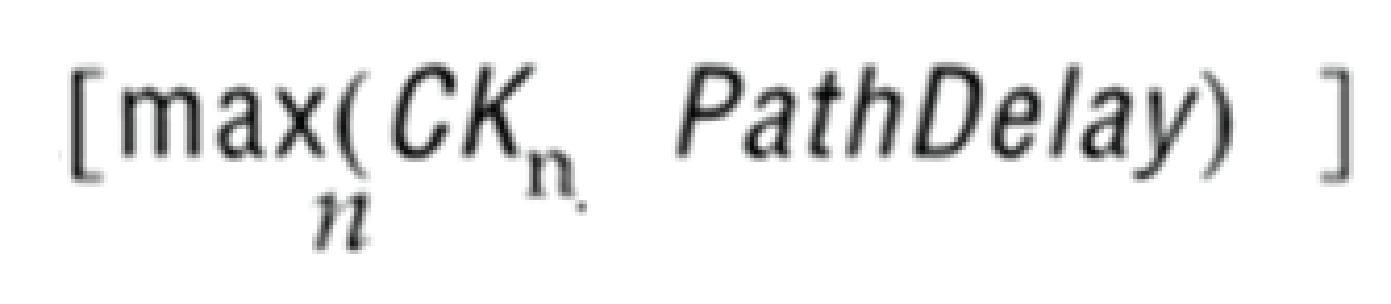

| Maximum CK delay to device | The delay of the longest CK trace from the FPGA to any device.

|

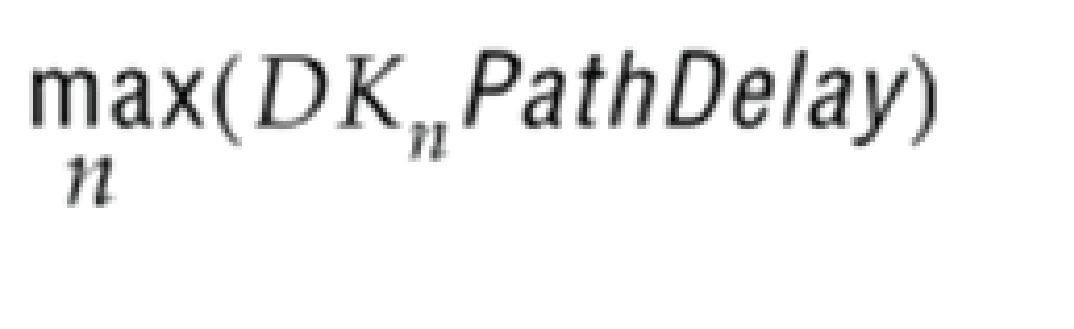

| Maximum DK delay to device | The delay of the longest DK trace from the FPGA to any device.

|

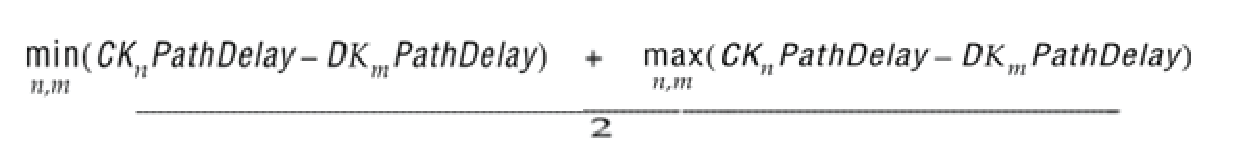

| Average delay difference between DK and CK | The average delay difference between the DK signals and the CK signal, calculated by averaging the longest and smallest DK delay minus the CK delay. Positive values represent DK signals that are longer than CK signals and negative values represent DK signals that are shorter than CK signals. The Quartus Prime software uses this skew to optimize the delay of the DK signals to have appropriate setup and hold margins.

|

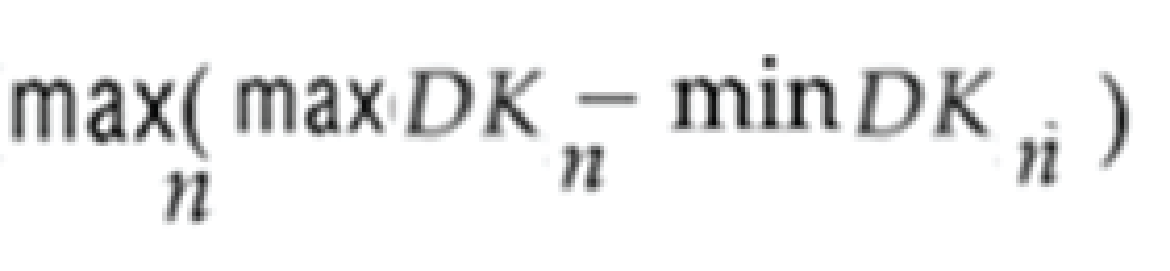

| Maximum skew between DK groups | The largest skew between DK signals in different DK groups.

|