Device-Specific Power Delivery Network (PDN) Tool 2.0 User Guide

ID

683293

Date

8/24/2021

Public

Visible to Intel only — GUID: hig1507663331843

Ixiasoft

1.2.2.1.1. Device Selection Section

1.2.2.1.2. Power Rail Data and Configuration Section

1.2.2.1.3. Meeting Target Impedance when Entering 0 A into the PDN Tool

1.2.2.1.4. Dealing with Multiple Shared Power Supply Pin Types

1.2.2.1.5. VRM Data Section

1.2.2.1.6. Rail Group Summary Section

1.2.2.1.7. VRM Impedance Section

1.2.2.1.8. BGA Via Section

1.2.2.1.9. Plane Section

1.2.2.1.10. Spreading Section

1.2.2.1.11. Implementing Split Planes

1.2.2.1.12. FEFFECTIVE Section

1.2.2.1.13. Decoupling Section

1.2.2.1.14. Results Summary Section

1.2.2.1.15. Recommended Flow for Deriving Decoupling for an FPGA System using the System_Decap Tab

Visible to Intel only — GUID: hig1507663331843

Ixiasoft

1.3.4. Further Optimizing for Better Accuracy

While the two methods described in Optimizing in Pre-Layout are mainly used in the pre-layout stage for a rough estimation of the decoupling solution, the method described here shows how to get a more accurate and optimized estimation.

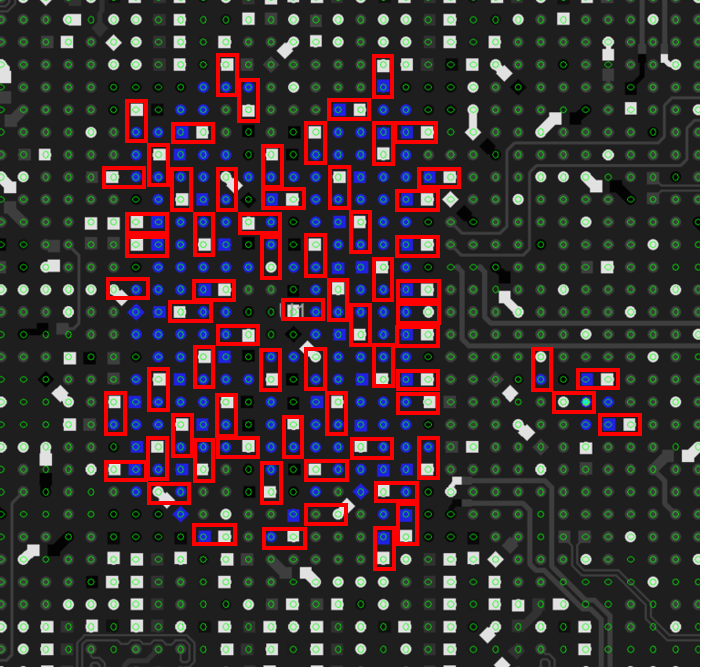

While Checking the Capacitor Model updates the decoupling capacitor library with the actual models used and Optimizing the Decap Count controls the number of decaps in manual mode, this method shows how to exclude Spreading R and L from the estimation process. As shown in the figure below, there is no mechanical restriction in populating decaps on the other side of the FPGA and red boxes indicate 70ea of 0402in decaps which can be directly placed; the majority of the total 124ea decaps can be populated right under BGAs. Thus, the spreading option might be negligible in this case.

Figure 38. Populating Decaps on the Other Side of the FPGA

- Change Feffective option from Calculate to Override.

- Check whether or not the number remains the same.

- If the number changes, write the recommended FEFFECTIVE, 10.18 MHz in the example below, into the white blank.

Figure 39. FEFFECTIVE Override

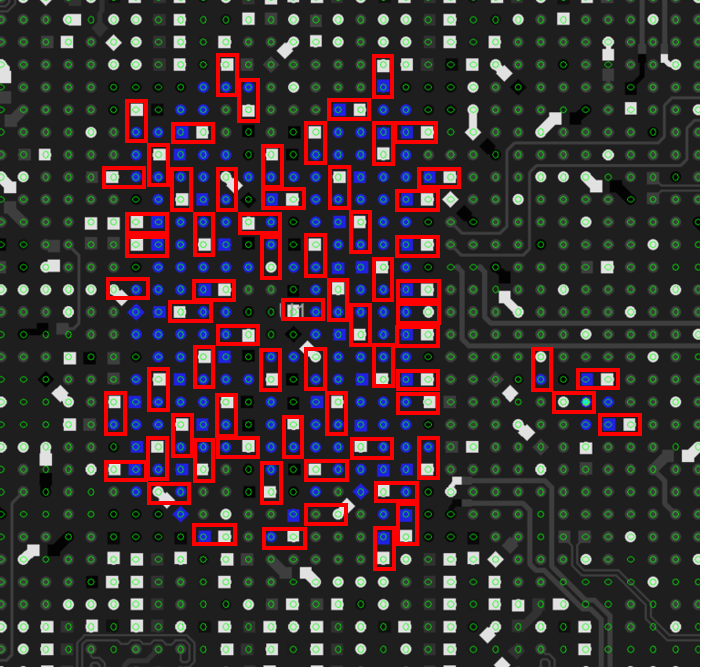

- Change the Spreading option from Low to Ignore.

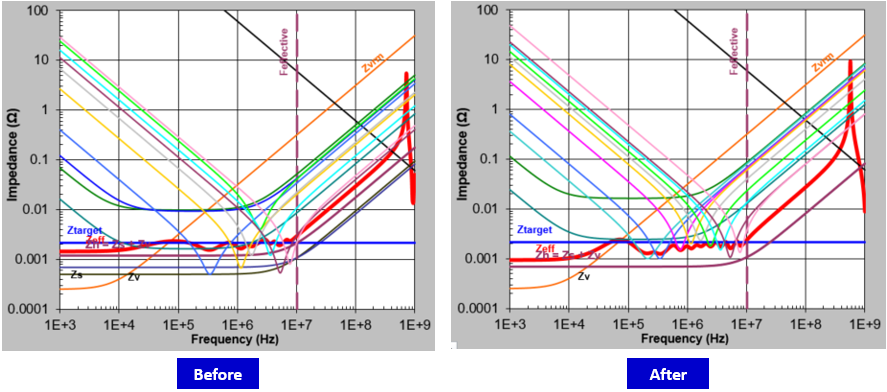

Once the spreading option is ignored, the entire ZPDN is lowered a little, which means more margin.Figure 40. Ignoring Spreading

- Repeat the manual optimization for each cap as shown in Optimizing the Decap Count.

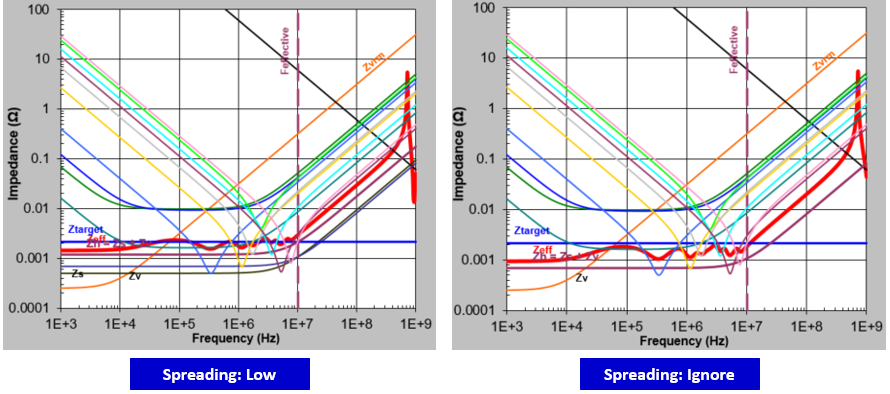

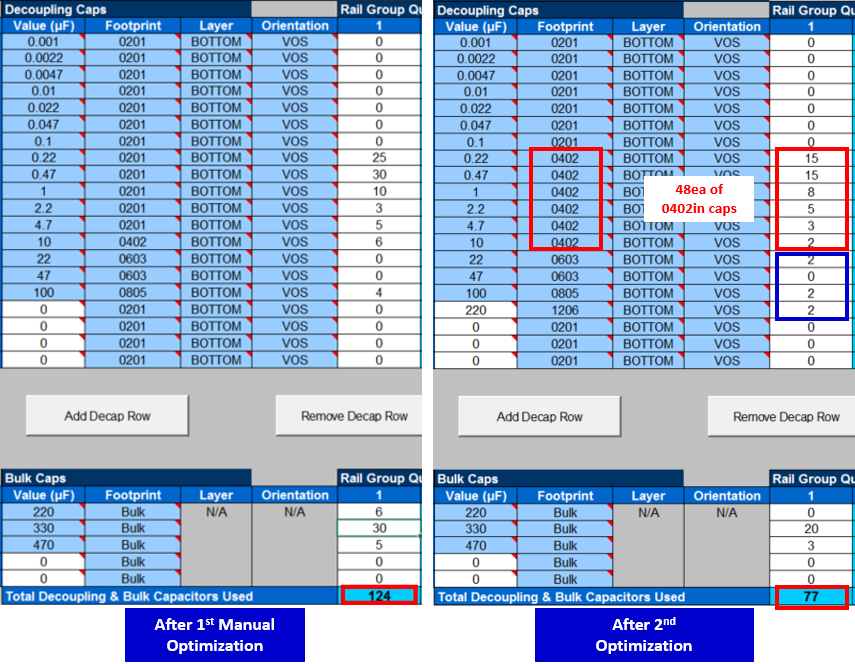

After the optimization process, only 48ea of 0402in capacitors (circled with a red box below) are estimated while the total allowable number of 0402in capacitors is 70ea. Also, the rest of the larger capacitors (circled with a blue box below) in this example can be populated in the BGA area. Final results are shown below. The total number of capacitors was decreased down to 77ea from the max limit of 301ea, including bulk capacitors, through round 1 and 2 of the optimization process.Note: The PDN tool result already includes the bulk capacitor solution for VRM. However, Intel recommends checking with the VRM vendor about the required output capacitance to check if the PDN tool estimation can cover the requirement. Intel® Enpirion® models in the VRM library already include the required output capacitance. For the required capacitor combination, please refer to the datasheet of each VRM model.Figure 41. Manual Decoupling Results Summary - Post-Optimization, Round 2

Related Information