Device-Specific Power Delivery Network (PDN) Tool 2.0 User Guide

Visible to Intel only — GUID: ile1506381119560

Ixiasoft

Visible to Intel only — GUID: ile1506381119560

Ixiasoft

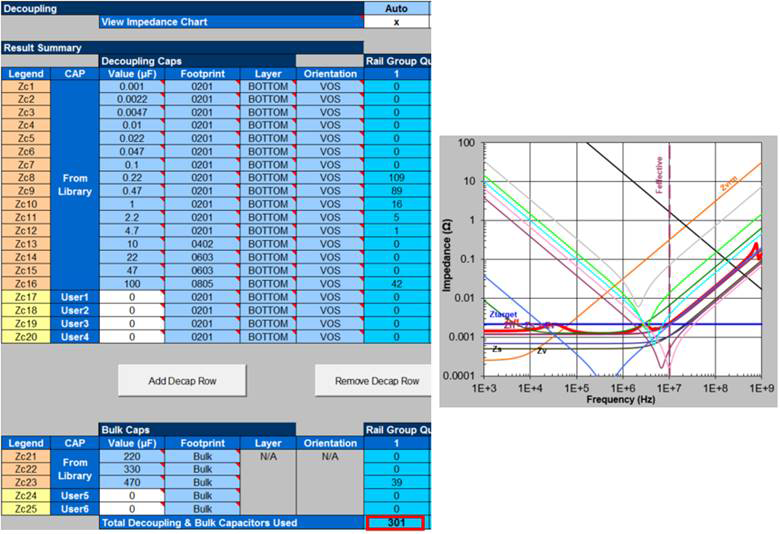

1.3.2.7. FEFFECTIVE and Decoupling Result Summary

The following figure shows final decoupling recommendations based on the inputs in the tool. However, even though ZPDN meets the ZTARGET up to FEFFECTIVE, the number of capacitors, 301, are not suitable for the real design. Refer to the Optimization Method section for details about optimizing your results.