Visible to Intel only — GUID: jfq1506360091688

Ixiasoft

1.2.2.1.1. Device Selection Section

1.2.2.1.2. Power Rail Data and Configuration Section

1.2.2.1.3. Meeting Target Impedance when Entering 0 A into the PDN Tool

1.2.2.1.4. Dealing with Multiple Shared Power Supply Pin Types

1.2.2.1.5. VRM Data Section

1.2.2.1.6. Rail Group Summary Section

1.2.2.1.7. VRM Impedance Section

1.2.2.1.8. BGA Via Section

1.2.2.1.9. Plane Section

1.2.2.1.10. Spreading Section

1.2.2.1.11. Implementing Split Planes

1.2.2.1.12. FEFFECTIVE Section

1.2.2.1.13. Decoupling Section

1.2.2.1.14. Results Summary Section

1.2.2.1.15. Recommended Flow for Deriving Decoupling for an FPGA System using the System_Decap Tab

Visible to Intel only — GUID: jfq1506360091688

Ixiasoft

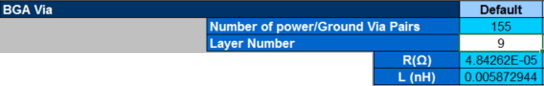

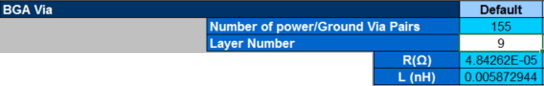

1.3.2.4. BGA Via

Once you select a power rail, the PDN tool automatically updates the number of Power/GND Via pairs. Every device has a different number.

The tool automatically calculates the parasitics when you enter your expected layer number in the Layer Number field by overriding for power rail location in the stackup.

Figure 28. BGA ViaThe Layer Number field also has the Ignore, Custom, and Calculate options.

Note: You can use the BGA_Via tab as a stand-alone tool for custom via parasitic calculation.