Visible to Intel only — GUID: vgu1711585746908

Ixiasoft

1. Introduction

2. Features

3. Getting Started with GTS AXI Streaming IP

4. IP Architecture and Functional Description

5. IP Parameters for E-Series FPGA

6. IP Parameters for D-Series FPGAs

7. Interfaces and Signals

8. Registers

9. Document Revision History for the GTS AXI Streaming Intel® FPGA IP for PCI Express* User Guide

A. Troubleshooting/Debugging

B. PIPE Mode Simulation

3.1. Downloading and Installing Quartus® Prime Software

3.2. Configuring and Generating the GTS AXI Streaming IP

3.3. Configuring and Generating GTS System PLL Clocks Intel® FPGA IP

3.4. Configuring and Generating GTS Reset Sequencer Intel® FPGA IP

3.5. Instantiating and Connecting GTS AXI Streaming IP Interfaces (and Other IPs)

3.6. Simulating the GTS AXI Streaming IP Variant

3.7. Compiling the GTS AXI Streaming IP Variant

4.1. Clocking

4.2. Resets

4.3. PCIe* Hard IP

4.4. Hard IP Interface (IF) Adaptor

4.5. Interrupts

4.6. Transaction Ordering

4.7. TX Non-Posted Metering Requirement on Application

4.8. AXI4-Stream Interface

4.9. Tag Allocation

4.10. Precision Time Measurement (PTM)

4.11. Single Root I/O Virtualization (SR-IOV)

4.12. Transaction Layer Packet (TLP) Bypass Mode

4.13. Scalable IOV

7.1. Overview

7.2. Clocks and Resets

7.3. AXI4-Stream Interfaces

7.4. Configuration Intercept Interface

7.5. Control Shadow Interface

7.6. Transmit Flow Control Credit Interface

7.7. Completion Timeout Interface

7.8. Control and Status Register Responder Interface

7.9. Function Level Reset Interface

7.10. TLP Bypass Error Reporting Interface

7.11. VF Error Flag Interface

7.12. Precision Time Measurement (PTM) Interface

7.13. Serial Data Signals

7.14. Miscellaneous Signals

8.6.1. VF PCI-Compatible Configuration Space Header Type0

8.6.2. VF PCI Express* Capability Structure

8.6.3. VF Message Signal Interrupt Extended (MSI-X) Capability Structure

8.6.4. VF Alternative Routing ID (ARI) Capability Structure

8.6.5. VF TLP Processing Hints (TPH) Capability Structure

8.6.6. VF Address Translation Services (ATS) Capability Structure

8.6.7. VF Access Control Services (ACS) Capability Structure

8.6.2.1. PCI Express* Capability List Register

8.6.2.2. PCI Express* Device Capabilities Register

8.6.2.3. PCI Express* Device Control and Status Register

8.6.2.4. Link Capabilities Register

8.6.2.5. Link Control and Status Register

8.6.2.6. PCI Express* Device Capabilities 2 Register

8.6.2.7. PCI Express* Device Control and Status 2 Register

8.6.2.8. Link Capabilities 2 Register

8.6.2.9. Link Control and Status 2 Register

Visible to Intel only — GUID: vgu1711585746908

Ixiasoft

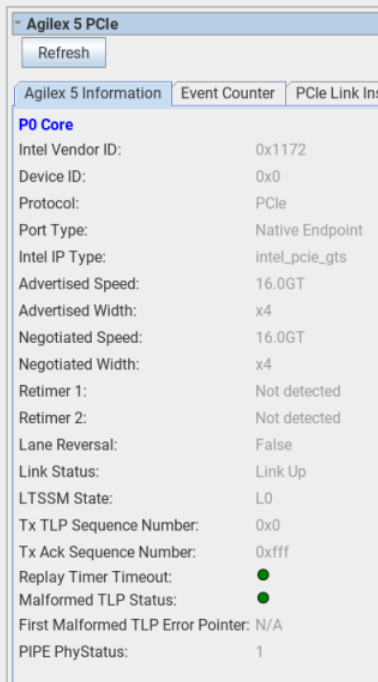

A.2.4.2.1. Agilex™ 5 Information

This lists a summary of the GTS AXI Streaming IP parameter settings in the GTS AXI Streaming IP parameter editor when the IP was generated, as read by the Agilex™ 5 Debug Toolkit when initialized.

All the information is read-only.

Use the Refresh button to read the settings.

| Parameter | Values | Descriptions |

|---|---|---|

| Intel Vendor ID | 1172 | Indicates the Vendor ID as set in the IP Parameter Editor. |

| Device ID | 0 | This is a unique identifier for the device that is assigned by the vendor. |

| Protocol | PCIe | Indicates the Protocol. |

| Port Type | Root Port, Endpoint 3 | Indicates the Hard IP Port type. |

| Intel IP Type | intel_pcie_gts | Indicates the IP type used. |

| Advertised speed | 8.0GT, 16.0GT | Indicates the advertised speed as configured in the IP Parameter Editor. |

| Advertised width | x4 | Indicates the advertised width as configured in the IP Parameter Editor. |

| Negotiated speed | 2.5GT, 5.0GT, 8.0GT, 16.0GT | Indicates the negotiated speed during link training. |

| Negotiated width | x4, x2, x1 | Indicates the negotiated link width during link training. |

| Link status | Link up, link down | Indicates if the link (DL) is up or not. |

| LTSSM State | Refer to Hard IP Status Interface | Indicates the current state of the link. |

| Lane Reversal | True, False | Indicates if lane reversal happens on the link. |

| Retimer 1 | Detected, not detected | Indicates if a retimer was detected between the Root Port and the Endpoint. |

| Retimer 2 | Detected, not detected | Indicates if a retimer was detected between the Root Port and the Endpoint. |

| Tx TLP Sequence Number | Hexadecimal value | Indicates the next transmit sequence number for the transmit TLP. |

| Tx Ack Sequence Timeout | Hexadecimal value | Indicates the ACK sequence number which is updated by receiving ACK/NAK DLLP. |

| Replay Timer Timeout | Green, Red | Green: no timeout Red: timeout |

| Malformed TLP Status | Green, Red | Green: no malformed TLP Red: malformed TLP detected |

| First Malformed TLP Error Pointer |

|

|

| PIPE PhyStatus |

0/1 |

Indicates the PMA and PCS are in reset mode. 0: PMA and PCS are out of reset 1: PMA and PCS are in reset |

Figure 75. Example of Agilex™ 5 Parameter Settings

3 The current version of Quartus® Prime supports enabling the Debug Toolkit for Endpoint mode only, and for the Linux and Windows operating systems only.