Visible to Intel only — GUID: jbt1719214853433

Ixiasoft

1. Introduction to the Agilex™ 5 Hard Processor System Component

2. Configuring the Agilex™ 5 Hard Processor System Component

3. Simulating the Agilex™ 5 HPS Component

4. Design Guidelines

5. HPS EMIF Platform Designer Example Designs

6. Document Revision History for the Hard Processor System Component Reference Manual Agilex™ 5 SoCs

2.1. Parameterizing the HPS Component

2.2. HPS-FPGA Interfaces

2.3. SDRAM

2.4. HPS Clocks, Reset, Power

2.5. I/O Delays

2.6. Pin Mux and Peripherals

2.7. Generating and Compiling the HPS Component

2.8. Using the Address Span Extender Component

2.9. Configuring the Agilex™ 5 Hard Processor System Component Revision History

2.2.1.1. Enable MPU Standby and Event Signals

2.2.1.2. Enable General Purpose Signals

2.2.1.3. Enable Debug APB* Interface

2.2.1.4. Enable System Trace Macrocell (STM) Hardware Events

2.2.1.5. Enable SWJ-DP JTAG Interface

2.2.1.6. Enable FPGA Cross Trigger Interface

2.2.1.7. Enable AMBA* Trace Bus (ATB)

3.1. Simulation Flows

3.2. Running the Simulation of the Design Examples

3.3. Clock and Reset Interface

3.4. FPGA-to-HPS AXI* Subordinate Interface

3.5. FPGA-to-SDRAM AXI* Subordinate Interface

3.6. HPS-to-FPGA AXI* Initiator Interface

3.7. Lightweight HPS-to-FPGA AXI* Initiator Interface

3.8. Simulating the Agilex™ 5 HPS Component Revision History

5.1. Terminology

5.2. Block Diagram

5.3. Version Support

5.4. Download Example Design Files

5.5. HPS EMIF Platform Designer Example Designs

5.6. Specific Examples

5.7. General Connection Guideline

5.8. Supported Memory Protocols Differences Among Intel SoC Device Families

5.9. IO96 Bank and Lane Usage for HPS EMIF

5.10. Quartus Report of I/O Bank Usage

Visible to Intel only — GUID: jbt1719214853433

Ixiasoft

5.6.1. DDR4 Examples

The following examples uses DDR4 in a design.

DDR4_1x16_1EMIF

The following examples show how to set up the HPS and EMIF components.

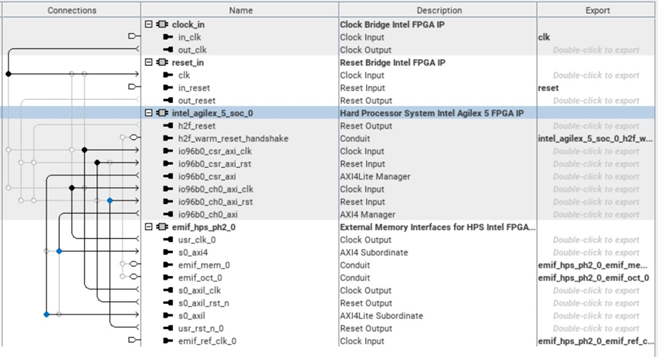

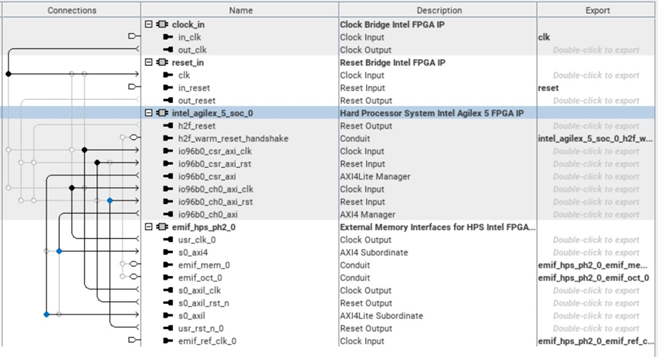

Figure 71. Graphical Connections DDR4_1x16_1EMIF

Figure 72. HPS Parameters DDR4_1x16_1EMIF

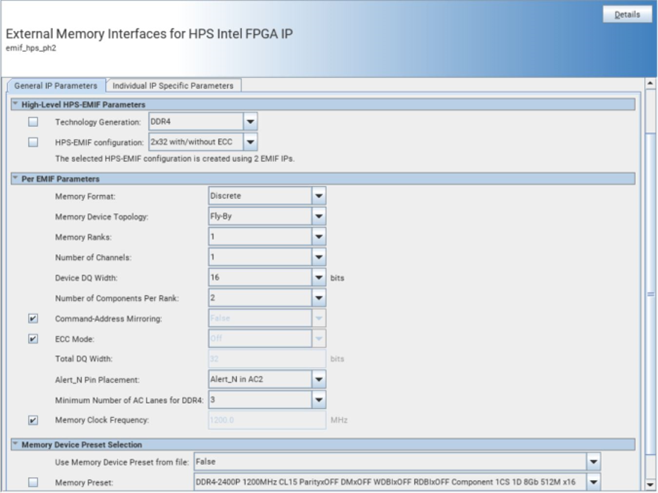

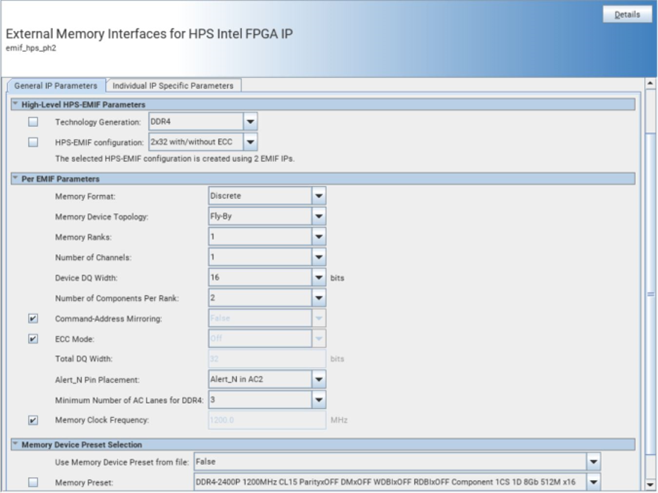

Figure 73. HPS EMIF Parameters DDR4_1x16_1EMIF

DDR4_1x16_ECC_1EMIF

The following examples show how to set up the HPS and EMIF components.

Figure 74. HPS EMIF Parameters DDR4_1x16_ECC_1EMIF

DDR4_1x32_1EMIF

The following examples show how to set up the HPS and EMIF components.

Figure 75. Graphical Connections DDR4_1x32_1EMIF

Figure 76. HPS Parameters DDR4_1x32_1EMIF

Figure 77. HPS EMIF Parameters DDR4_1x32_1EMIF

DDR4_1x32_ECC_1EMIF

The following examples show how to set up the HPS and EMIF components.

Figure 78. HPS EMIF Parameters DDR4_1x32_ECC_1EMIF

DDR4_2x32_2EMIF

The following examples show how to set up the HPS and EMIF components.

Figure 79. Graphical Connections DDR4_2x32_2EMIF

Figure 80. HPS Parameters DDR4_2x32_2EMIF

Figure 81. HPS EMIF Parameters DDR4_2x32_2EMIF

DDR4_2x32_ECC_2EMIF

The following examples show how to set up the HPS and EMIF components.

Figure 82. HPS EMIF Parameters DDR4_2x32_ECC_2EMIF