Visible to Intel only — GUID: lbj1666021005839

Ixiasoft

Visible to Intel only — GUID: lbj1666021005839

Ixiasoft

3.2.2. Memory Subsystem TCAM

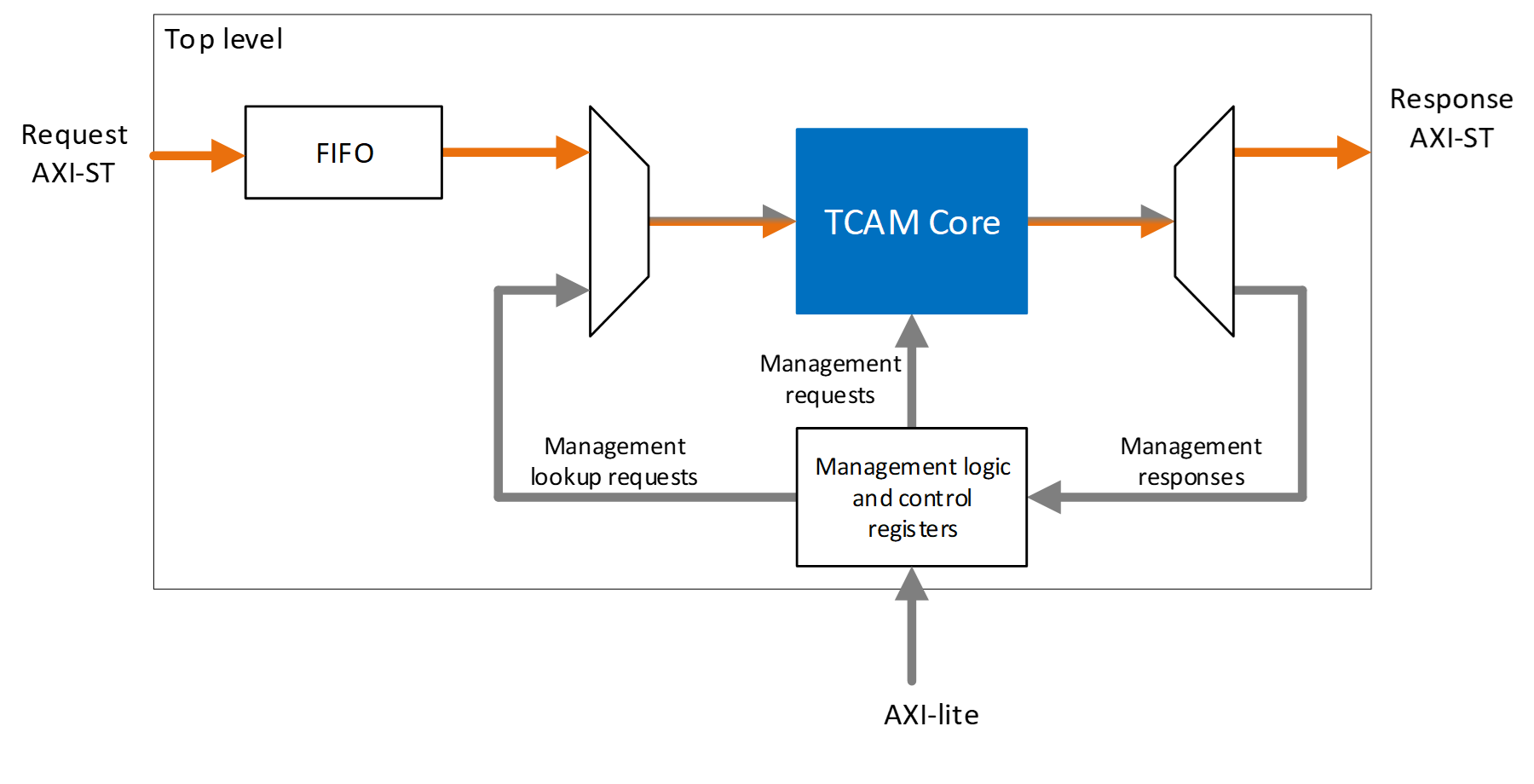

An AXI-Lite interface allows a CPU to insert, delete or flush (delete all) database entries, and also allows the CPU to search for a specific key. To insert an entry, the CPU must specify the entry ID, the key, a corresponding mask (indicating which key bits to check during a search) and an optional result field. If a key matches multiple entries during a search, the highest matching entry ID is output, along with the optional result field.

The masking is fully flexible – there are no limitations on the mask values or on the number of unique masks that can be used.

You can configure each TCAM with up to 4 core tables, which can make time-multiplexed requests to memory blocks. The TCAM can achieve up to 1 search-per-cycle using pipelined execution when it is configured with only 1 core table, when the TCAM is generated with more than 1 core table and the request rate is higher than the throughput, the pending requests are stored in a FIFO buffer.

The control part of the system accepts management requests to and from a CPU using the AXI-Lite registers and performs all necessary operations to process those requests. The management requests perform operations on the database such as flush, insert, delete, or search entries.