Visible to Intel only — GUID: edl1693483440495

Ixiasoft

Visible to Intel only — GUID: edl1693483440495

Ixiasoft

8.2.5. Parameterizing Required EMIF, CAM, and MSA IPs

The sub-IPs within the memory subsystem are as follows:

- External memory interface (EMIF) IP

- MSA IP

- EMIF for HPS IP

- CAM IPs (BCAM, TCAM, MBL)

To parameterize the sub-IPs, proceed as follows:

- Check the Generate IPs within Memory Subsystem checkbox.

- Click Dive Into Packaged Subsystem. A new Platform Designer window appears, listing the necessary controls to allow you to parametrize and fine-tune all the IPs that are part of the Memory Subsystem IP.

- Use the Platform Designer window to parameterize the individual IPs. Refer to the following topics for details.

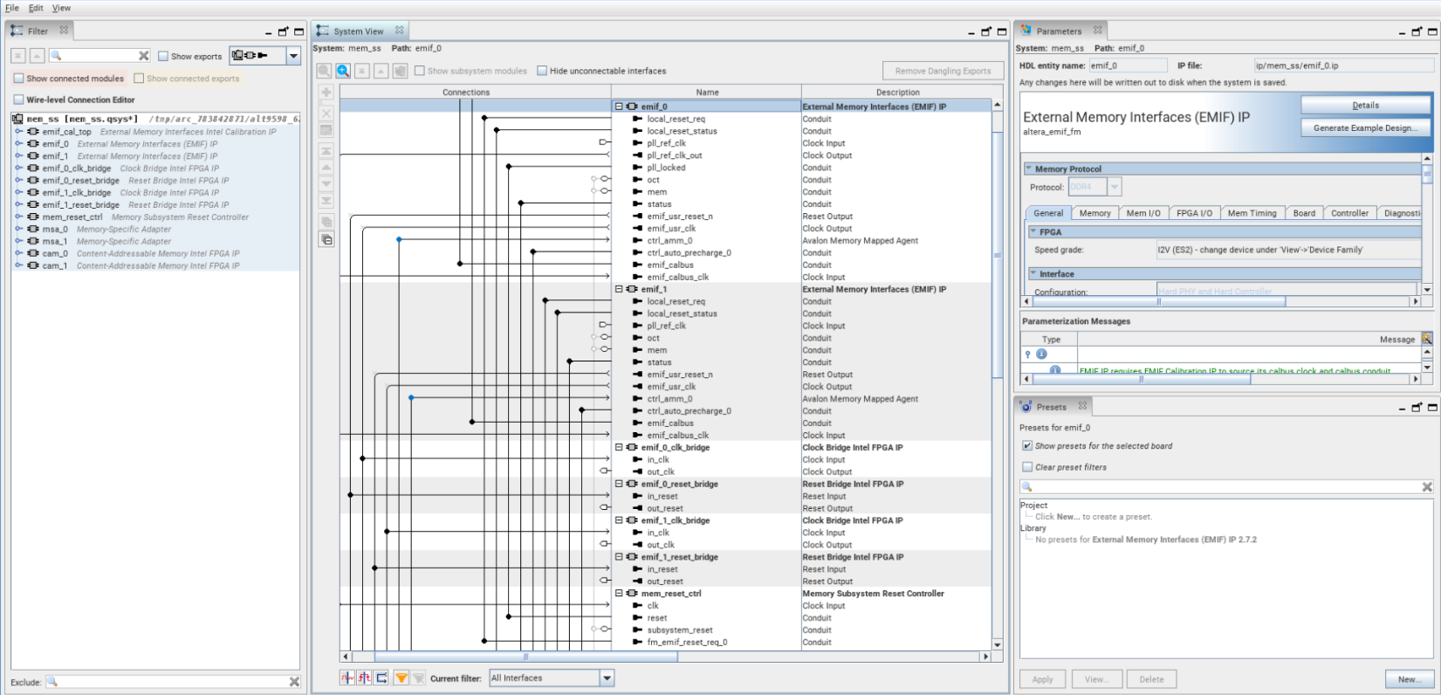

The following figure depicts the Platform Designer window:

The Filter tab provides a quick overview of all instantiated IPs that are part of your memory subsystem IP. This figure is a continuation of the example discussed in the previous topics, and shows the expected IPs: one calibration IP for both EMIF IPs, their two associated MSA IPs, and two CAM IPs.

The following table shows how the configured high-level topology is translated to all the listed IPs:

| High-Level Topology | Associated IPs | ||

|---|---|---|---|

| Memory Interface | Application Interface | Main IPs | Calibration, Reset, and Bridge IPs |

| External: DDR4 | Storage | emif_0, msa_0 | emif_cal_top, emif_0_clk_bridge, emif_0_reset_bridge, mem_reset_ctrl |

| On-chip: M20K | Associative storage | cam_0 | |

| External: DDR4 | Associative storage | emif_1, msa_1, cam_1 | emif_cal_top, emif_1_clk_bridge, emif_1_reset_bridge, mem_reset_ctrl |

Section Content

Parameterizing the External Memory Interface (EMIF) IP

Parameterizing the Memory-Specific Adapter

Parameterizing the Content-Addressable Memory (CAM) IP

Parameterizing the External Memory Interfaces Calibration IP

Saving the IPs Within the Memory Subsystem

Propagation of Changes Across IPs within the Memory Subsystem IP