Visible to Intel only — GUID: GUID-5F80B30D-8C9C-43C8-A92F-2EFFC2545F25

Visible to Intel only — GUID: GUID-5F80B30D-8C9C-43C8-A92F-2EFFC2545F25

Global Memory Accesses Optimization

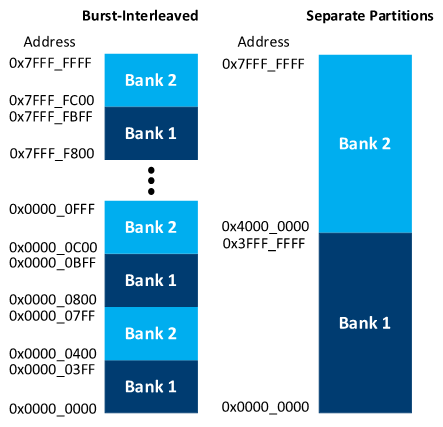

The Intel® oneAPI DPC++/C++ Compiler uses SDRAM as global memory. By default, the compiler configures global memory in a burst-interleaved configuration. The Intel® oneAPI DPC++/C++ Compiler interleaves global memory across each of the external memory banks.

In most circumstances, the default burst-interleaved configuration leads to the best load balancing between memory banks. However, in some cases, you might want to partition the banks manually as two non-interleaved (and contiguous) memory regions to achieve better load balancing.

The following figure illustrates the difference in memory mapping patterns between burst-interleaved and non-interleaved memory partitions:

- Global Memory Bandwidth Use Calculation

- Manual Partition of Global Memory

- Partitioning Buffers Across Different Memory Types (Heterogeneous Memory)

- Partitioning Buffers Across Memory Channels of the Same Memory Type

- Ignoring Dependencies Between Accessor Arguments

- Contiguous Memory Accesses

- Static Memory Coalescing