Visible to Intel only — GUID: sth1424974656172

Ixiasoft

3.11. The Clock Control

The MAX® 10 FPGA development board Clock Control application sets the programmable oscillators to any frequency between 10 MHz and 810 MHz. The frequencies support eight digits of precision to the right of the decimal point.

The Clock Control communicates with the MAX II device on the board through the JTAG bus. The programmable oscillators are connected to the MAX II device through a 2-wire serial bus.

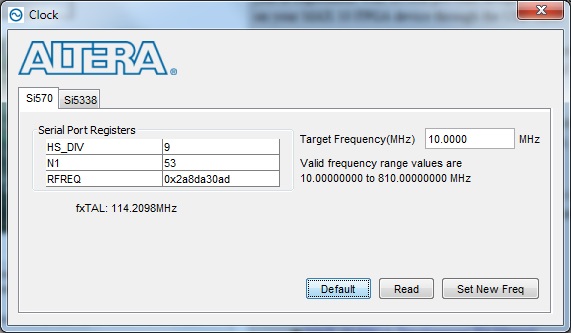

Figure 16. The Si570 Tab

| Control | Description |

|---|---|

| Serial Port Registers | Shows the current values from the Si570 registers for frequency configuration. |

| Target frequency (MHZ) | Allows you to specify the frequency of the clock. Legal values are between 10 and 810 MHz with eight digits of precision to the right of the decimal point. For example, 421.31259873 is possible within 100 parts per million (ppm). The Target frequency control works in conjunction with the Set New Freq control. |

| fXTAL | Shows the calculated internal fixed-frequency crystal, based on the serial port register values. |

| Default | Sets the frequency for the oscillator associated with the active tab back to its default value. This can also be accomplished by power cycling the board. |

| Read | Reads the current frequency setting for the oscillator associated with the active tab. |

| Set New Freq | Sets the programmable oscillator frequency for the selected clock to the value in the Target frequency control for the programmable oscillators. Frequency changes might take several milliseconds to take effect. You might see glitches on the clock during this time. Altera recommends resetting the FPGA logic after changing frequencies. |

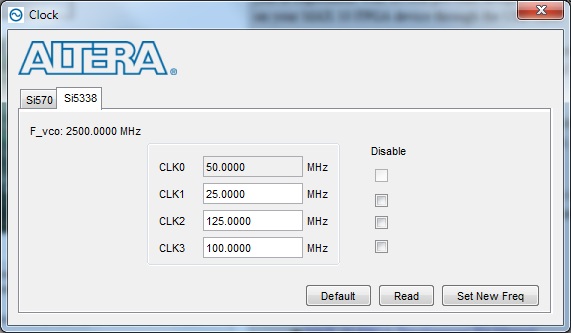

Figure 17. The Si5338 Tab

| Control | Description |

|---|---|

| F_vco | Displays the generating signal value of the voltage-controlled oscillator. |

| Registers | Display the current frequencies for each oscillator. |

| Frequency (MHz) | Allows you to specify the frequency of the clock. |

| Disable | Disable each oscillators as required. |

| Read | Reads the current frequency setting for the oscillator associated with the active tab. |

| Default | Sets the frequency for the oscillator associated with the active tab back to its default value. This can also be accomplished by power cycling the board. |

| Set New Freq | Sets the programmable oscillator frequency for the selected clock to the value in the CLK0 to CLK3 controls. Frequency changes might take several milliseconds to take effect. You might see glitches on the clock during this time. Altera recommends resetting the FPGA logic after changing frequencies.

Note: Changing CLK0 of Si5338 will affect the Clock/Power GUI. One clock from port CLK0 is used to drive the MAX II device which as a 2-wire serial bus interface connected to SI570, Si5338, and the power monitor.

|