Visible to Intel only — GUID: eni1547144160923

Ixiasoft

Visible to Intel only — GUID: eni1547144160923

Ixiasoft

5.2. Simulation Walkthrough

A given design may display different latency values on different boards, due to differences in board implementation.

The Intel® Agilex™ EMIF IP supports functional simulation only. Functional simulation is supported at the RTL level after generating a post-fit functional simulation netlist. The post-fit netlist for designs that contain Intel® Agilex™ EMIF IP is a hybrid of the gate level (for FPGA core) and RTL level (for the external memory interface IP). You should validate the functional operation of your design using RTL simulation, and the timing of your design using timing analysis.

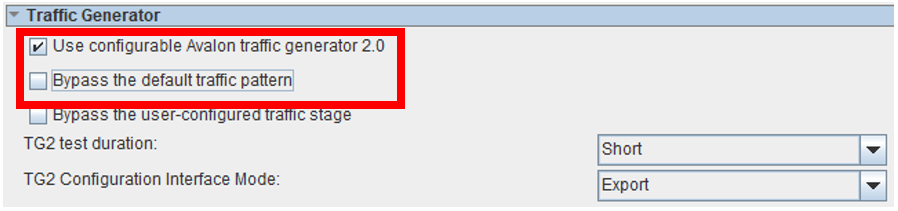

The Intel® Agilex™ EMIF IP supports functional simulation through the design example using the Traffic Generator (TG1) or the Traffic Generator 2.0 (TG2). TG2 is a configurable traffic generator. (For information on TG2, refer to Configurable Traffic Generator (TG2) Description. Functional simulation using TG2 is allowed both in default traffic pattern and user configured traffic mode. In default traffic mode, TG2 runs a default traffic pattern after reset instead of waiting for user configuration for TG2; whereas user mode allows you to provide your own custom traffic. Do not select Bypass the default traffic pattern when creating a design example for functional simulation using TG2 default traffic mode. For more information on simulating with TG2 in user configured traffic mode, refer to Configuration and Status Registers.

To perform functional simulation for an Intel® Agilex™ EMIF IP design example, locate the design example files in the design example directory.

You can use the IP functional simulation model with any supported VHDL or Verilog HDL simulator.

After you have generated the memory IP, you can locate multiple file sets for various supported simulations in the sim/ed_sim subdirectory. For more information about the EMIF simulation design example, refer to the Intel® Agilex™ External Memory Interfaces IP Design Example User Guide.