Visible to Intel only — GUID: uon1547134061436

Ixiasoft

Visible to Intel only — GUID: uon1547134061436

Ixiasoft

10.4.3. Bank Interleaving

- Page size refers to the minimum number of column locations on any row that you access with a single activate command.

- For DDR4, bank refers to a bank address and a bank group.

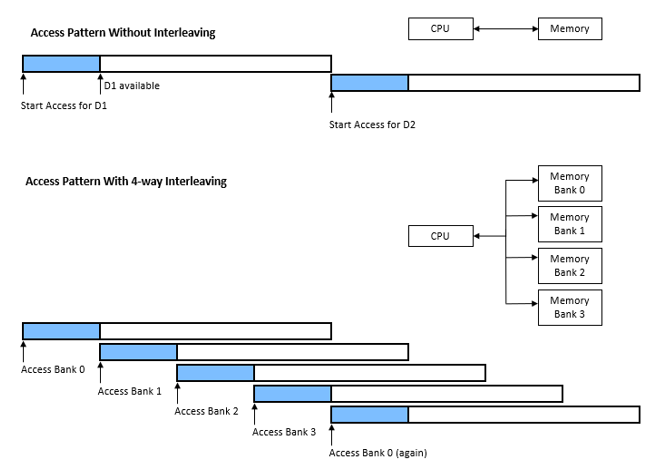

Without interleaving, the controller sends the address to the SDRAM device, receives the data requested, and then waits for the SDRAM device to precharge and reactivate before initiating the next data transaction, thus wasting several clock cycles.

Interleaving allows banks of the SDRAM device to alternate their background operations and access cycles. One bank undergoes its precharge/activate cycle while another is being accessed. By alternating banks, the controller improves its performance by masking the precharge/activate time of each bank. If there are four banks in the system, the controller can ideally send one data request to each of the banks in consecutive clock cycles.

For example, in the first clock cycle, the CPU sends an address to Bank 0, and then sends the next address to Bank 1 in the second clock cycle, before sending the third and fourth addresses to Banks 2 and 3 in the third and fourth clock cycles respectively. The sequence is as follows:

- Controller sends address 0 to Bank 0.

- Controller sends address 1 to Bank 1 and receives data 0 from Bank 0.

- Controller sends address 2 to Bank 2 and receives data 1 from Bank 1.

- Controller sends address 3 to Bank 3 and receives data 2 from Bank 2.

- Controller receives data 3 from Bank 3.

The following figure shows how you can use interleaving to increase bandwidth.

The controller supports three interleaving options:

CS-BG-Bank-CID-Row-Col – This is a non-interleaved option. Select this option to improve efficiency with random traffic

CS-CID-Row-Col-Bank-BG – This option uses bank interleaving without chip select interleaving. Select this option to improve efficiency with sequential traffic, by spreading smaller data structures across all banks in a chip.

CID-Row-CS-Bank-Col-BG – This option uses bank interleaving with chip select interleaving. Select this option to improve efficiency with sequential traffic and multiple chip selects. This option allows smaller data structures to spread across multiple banks and chips.

Bank interleaving is a fixed pattern of data transactions, enabling best-case bandwidth and latency, and allowing for sufficient interleaved transactions between opening banks to completely hide tRC. An optimal system can achieve 100% efficiency for bank interleave transactions with 8 banks. A system with less than 8 banks is unlikely to achieve 100%.