Visible to Intel only — GUID: skj1682961658264

Ixiasoft

Visible to Intel only — GUID: skj1682961658264

Ixiasoft

3. Agilex™ 5 MIPI D-PHY Architecture

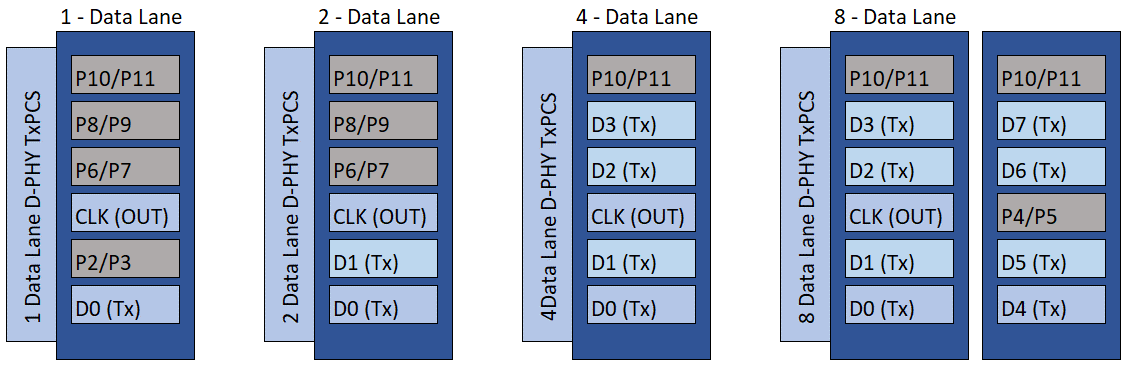

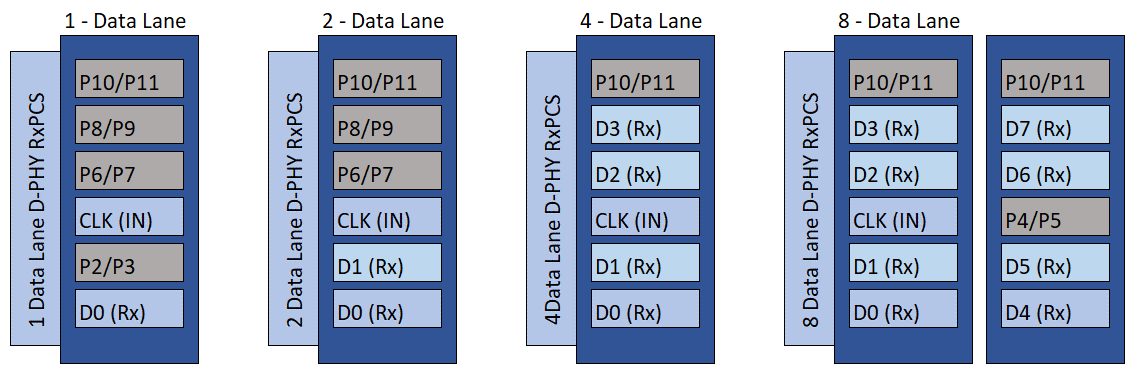

Agilex™ 5 supports MIPI D-PHY through HSIO banks. Each HSIO bank consists of 8 byte blocks to support MIPI D-PHY; however, one byte blocks is reserved for RZQ calibration and reference clock. Therefore the maximum MIPI D-PHY that a single HSIO bank can support is up to 7 interfaces (subject to D-PHY lanes configuration). The Agilex™ 5 D-PHY offers a native D-PHY interface that allows direct point-to-point connection between the D-PHY transmitter and D-PHY receiver without any passive circuitry or third-party component in between. Each interface can support 1, 2, 4, or 8 data lanes plus 1 clock lane.

Each interface has prefixed data lane and clock lane placement as illustrated in the diagram below. Refer to the MIPI D-PHY Interface Implementation section to understand the implementation and how to identify the physical pin placement.