Visible to Intel only — GUID: jaj1682964542926

Ixiasoft

Visible to Intel only — GUID: jaj1682964542926

Ixiasoft

3.3. Initialization and Reset Sequences

An asynchronous system reset is required to initialize the PCS soft logic to a known good state. This system reset is internally gated with the PLL lock signal to guarantee that the logic comes out of reset only when the clocks are stable.

The initialization flow for both TX and RX modes is as follows:

- PLL achieves LOCK.

- INIT_DONE is asserted.

- PPI.Enable for the active lanes are asserted.

- Register D-PHY_CSR.Enable is set to ‘1’ (DEFAULT).

The D-PHY IP has a programmable register tINIT that allows the soft IP to implement the initialization sequence. The initialization states for both the D-PHY TX and RX mode are as follows:

| Mode | State | Exit State | Exit Condition | Line Levels |

|---|---|---|---|---|

| TX | OFF/RESET | TX_INIT | Reset_n deasserted & PLL locked & PPI Enabled . | Not LP-11 |

| TX | TX_INIT | TX_READY | A first stop state for a period longer than tINIT timeout as specified by the protocol. Init_done is asserted | LP-11 |

| TX | TX_READY | RESET | Reset_n asserted or PLL unlocked or PPI disabled | Active |

| RX | OFF/RESET | RX_INIT | Reset_n deasserted & PLL locked & PPI Enabled | Any |

| RX | RX_INIT | RX_READY | Observe LP11 for tINIT | LP-11 |

| RX | RX_READY | RESET | Reset_n asserted or PLL unlocked or PPI disabled | Active |

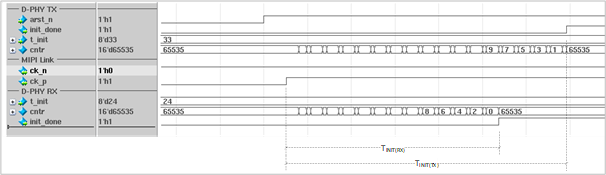

The following is a timing diagram for the initialization sequence for both D-PHY TX and D-PHY RX modes.

Each clock domain has both a synchronous and asynchronous reset. These signals are generated internally from the incoming system reset (gated with PLL lock) and D-PHY link’s PPI.Enable signal for data lane 0 properly synchronized to the destination clock domains.

The register interface uses the synchronous reset input port srst_axil_n. This reset domain is totally independent of the rest of the logic with no dependency on the system reset, PLL lock or init_done signals.