Visible to Intel only — GUID: uzt1683041658977

Ixiasoft

Visible to Intel only — GUID: uzt1683041658977

Ixiasoft

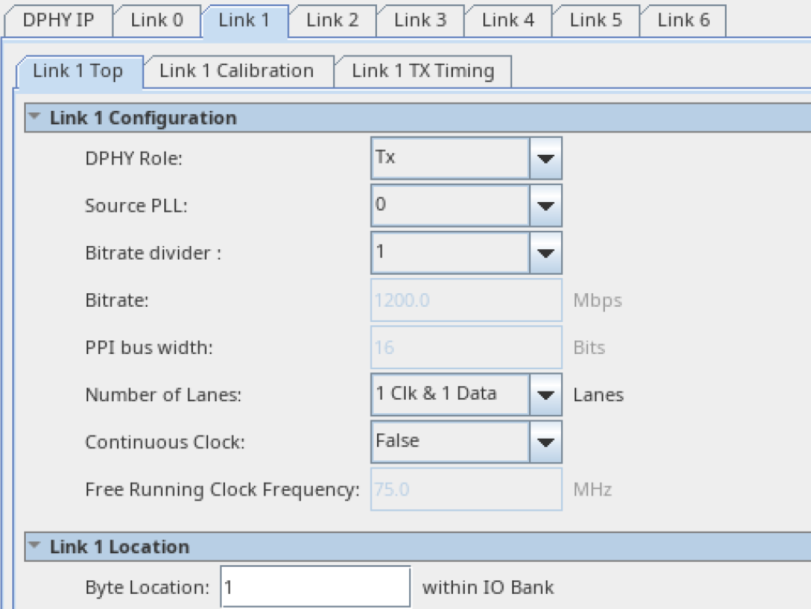

5.4. Configuring the MIPI D-PHY TX Mode

You need to specify the MIPI D-PHY link location on the I/O bank during IP configuration. Look for the Byte Location parameter under the Link n Location for each Link n tab. For the physical pin location of each byte location, refer to the table in the Identifying Pin Assignments Based on Byte Location topic.

| Parameter Name | Description | Setting |

|---|---|---|

| D-PHY Role | Configure D-PHY mode as Tx or Rx. | Unused, TX, or RX. (Default is Unused.) |

| Source PLL | Specify which PLL source will drive the link's clock. | 0 or 1. (Default value is 0.) |

| Bit Rate Divider | Bit rate divider to keep VCO > 600MHz. Used to divide the TX bit rate. | 1, 2, 4, or 8. (Default value is 8.) |

| Bit Rate | Not available for Tx mode. | D-Series: 150Mbps - 3500Mbps E-Series device group A: 150Mbps - 3500Mbps E-Series device group B: 150Mbps - 2500Mbps |

| PPI bus width | Not available for Tx mode. | 16. |

| Number of Lanes | Set number of data lanes for the link : 1, 2, 4 or 8. | 1 Data & 1 Clk 2 Data & 1 Clk 4 Data & 1 Clk 8 Data & 1 Clk (Default is 1 Data & 1 Clk.) |

| Continuous clock | Specify that the clock lane is continuous. | True or False. (Default value is False.) |

| Free Running Clock Frequency | Not available for Tx mode. | |

| Byte location | Specifies D-PHY links BYTE location within the I/O bank. | 0-7. |

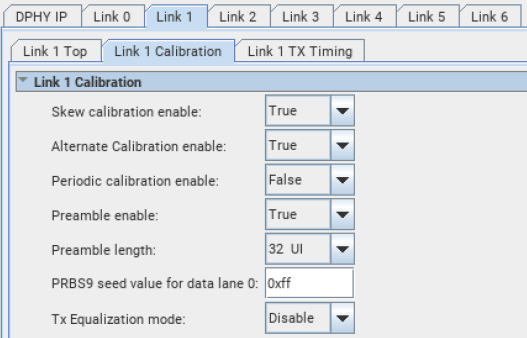

Link Calibration Configuration

On the Link Calibration tab you can enable the skew, alternate, and periodic calibration functions, preamble and TX equalization mode to meet your performance requirements. You can run simulation to validate which TX equalization mode suits your design intent. For data rates above 2.0G, you should set the TX equalization mode to MED LP on Quartus® Prime Pro Edition software version 24.2; if you are using version 24.1, select mode 1.

| Parameter Name | Description | Setting |

|---|---|---|

| Skew Calibration Enable | Generate logic to support skew calibration. | True or False. (Default value is False.) |

| Alternate Calibration Enable | Generate logic to support alternate calibration (Show when skew calibration enabled). | True or False. (Default value is False.) |

| Periodic calibration enable | Generate logic to support periodic skew calibration (Show when skew calibration enabled). | True or False. (Default value is False.) |

| Preamble Enabled | Generate logic to support preamble. | True or False. (Default value is False.) |

| Preamble Length | Preamble length settings (when Preamble is enabled). | 32,64,96,128,160,192,224,256,288,320,352,384,416,448,480,512 UI. (Default value is 32.) |

| PRBS9 seed value for data lane n | PRBS value for data lane used by Tx / Rx alt cal and test mode. (Available when Alternate Calibration is enabled.) | 0xFF |

| Tx equalization mode | Tx Equalization mode. | Disable or MED LP or HI LP or MED CZ. (Default value is Disable.) |

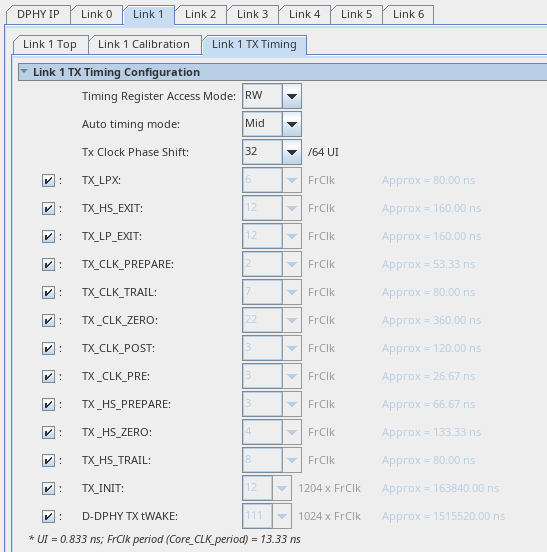

Link TX Timing Parameters

On the Link TX Timing tab you can configure the transmit timing parameters..

| Parameter Name | Description | Setting |

|---|---|---|

| Timing Register Access Mode | Set to implement timing registers as R/W or RO. R/W register will use up more FPGA resources. | RW or RO. (Default value is RW.) |

| Auto Timing mode | Choose to use min timing, max timing or mid for default values of timing registers set to "Auto". All timing registers have a min specified timing, but not all have a max specified timing. For those with no max specified timing, max Is set to register max value. | Max or Mid or Min. (Default value is Mid.) |

| TX Clock Phase Shift | Sets the phase shift of the clock lane relative to the data lanes. 1 UI is equivalent to 64 steps. Default is 32, shifting clock by 1/2 UI. | 0-63. (Default value is 32.) |

| TX_LPX | Transmitted length of any Low-Power state period. TLPX is an internal PHY timing parameter. TCLK-PREPARE is an external parameter, which can differ from TLPX. | 0-128. (Default value is 6.) |

| TX_HS_Exit | Time that the transmitter drives LP-11 following a HS burst. | 0-255. (Default value is 12.) |

| TX_LP_Exit | Time that the transmitter drives LP-11 between any LP sequences, or between an LP sequence and a HS burst. | 0-255. (Default value is 12.) |

| Tx_CLK_Prepare | Time that the transmitter drives the Clock Lane LP-00 Line state immediately before the HS-0 Line state starting the HS transmission. Delay computation (approx): TCLK-PREPARE = (TX_CLK_PREPARE + 2) * Core_CLK_period. | 0-63. (Default value is 2.) |

| Tx_Clk_Trail | Time that the transmitter drives the HS-0 state after the last payload clock bit of a HS transmission burst. Delay computation (approx): TCLK-TRAIL = (TX_CLK_TRAIL - TXFIFO_LAT) * Core_CLK_period where TXFIFO_LAT might be different for PPI = 16 and 8. | 0-127. (Default value is 7.) |

| Tx_clk_zero | Time that the transmitter drives the HS-0 state prior to starting the Clock. Delay computation (approx): (+ TXFIFO_LAT is intended) TCLK-ZERO = (TX_CLK_ZERO + 2 + TXFIFO_LAT) * Core_CLK_period. | 0-127. (Default value is 22.) |

| Tx_clk_Post | Time that the transmitter continues to send HS clock after the last associated Data Lane has transitioned to LP mode. Interval is defined as the period from the end of THS-TRAIL to the beginning of TCLK-TRAIL. Delay computation (approx) : (+ TXFIFO_LAT is intended) TCLK-POST = (TX_CLK_POST + 2 + TXFIFO_LAT - (2*TX_VCO_FREQ_MULT)) * Core_CLK_period. TX_VCO_FREQ_MULT is the Bit Rate Divider value described on table 14 to target Low Bit Rate speeds on our RX IP. | 0-255. (Default value is 3.) |

| Tx_CLK_Pre | Time that the HS clock shall be driven by the transmitter prior to any associated Data Lane beginning the transition from LP to HS mode. Delay computation: TCLK-PRE = (TX_CLK_PRE + 2 - TXFIFO_LAT) * Core_CLK_period Aligned to data lanes' next ESC clock edge. | 0-15. (Default value is 3.) |

| Tx_HS_Prepare | Time that the transmitter drives the Data Lane LP-00 Line state immediately before the HS-0 Line state starting the HS transmission. Delay computation (approx): THS-PREPARE = (TX_HS_PREPARE + 2) * Core_CLK_period. | 0-63. (Default value is 3.) |

| Tx_HS_Zero | Time that the transmitter drives the HS-0 state prior to transmitting the Sync sequence. Delay computation (approx): (+ TXFIFO_LAT is intended) THS-ZERO = (TX_HS_ZERO + 4 + TXFIFO_LAT ) * Core_CLK_period. | 0-255. (Default value is 4.) |

| Tx_HS_Trail | Time that the transmitter drives the flipped differential state after last payload data bit of a HS transmission burst. Delay computation (approx): THS-TRAIL = (TX_HS_TRAIL + 1 - TXFIFO_LAT - (TX_VCO_FREQ_MULT > 2 ? 8 : 2) ) * CORE_CLK_period. TX_VCO_FREQ_MULT is the Bit Rate Divider value described on table 14 to target Low Bit Rate speeds on our RX IP. | 0-255. (Default value is 8.) |

| Tx_Init | Time that Slave side PHY shall be initialized when the Master PHY drives a Stop State. | 0-255. (Default value is 12.) |

| D-PHY Tx Twake | Time that a transmitter drives a Mark-1 state prior to a Stop state in order to initiate an exit from ULPS. | 0-255. (Default value is 111.) |