Visible to Intel only — GUID: qbg1707412752394

Ixiasoft

Visible to Intel only — GUID: qbg1707412752394

Ixiasoft

4.7. MIPI Interface Layout Design Guidelines

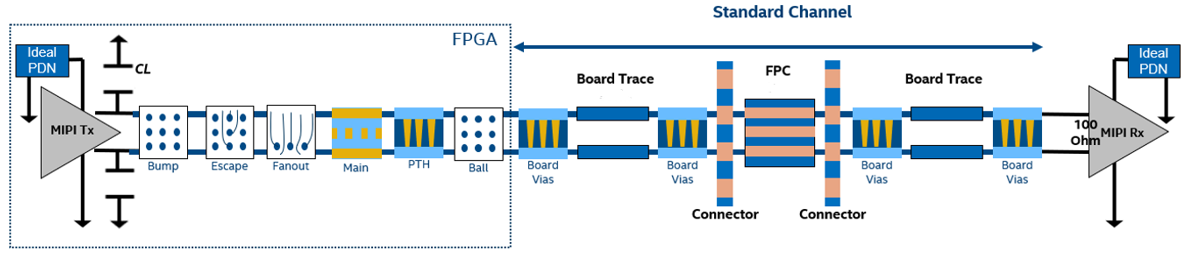

In the MIPI design, board traces, vias, connectors and cables are considered to be part of the board specification, while silicon and package are excluded. The following figure shows the supported standard reference channel up to 3.5Gbps with respect to the maximum board trace length.

To meet the MIPI standard electrical specification on a MIPI interface, board designers must follow these guidelines:

- The signal trace impedance on board is recommended to be 100-ohm differential. If the differential channel is also used for LP single-ended signal, it is recommended to apply loosely coupled differential transmission line.

- Altera recommends using backdrill or micro via to minimize the impact of stub on signal transition vias, if performance is not good after the channel simulation.

- Skew matching must be controlled within +/-50 mil between data to clock signals.

- In addition, keep 3 x h for intra-pair spacing while 5 x h for inter-pair spacing.

- Avoid routing noisy signals such as CLK signals or VR modules near to MIPI signals; also, avoid having MIPI signals reference plane to a noisy power plane.

The supported MIPI data rate varies based on two different MIPI board trace settings (length):

- Long reference channel on PCB is supported up to 2.5Gbps.

- Standard reference channel is supported up to 3.5Gbps.

| Data Rate (Gbps) | 2.5 | 3.5 |

|---|---|---|

| Supported Reference Channel | Long | Standard |

| Insertion Loss Frequency at 1.25GHz | -6.3dB ±0.5 dB | -3.75dB ±0.5 dB |

| Insertion Loss Frequency at 5GHz | -20dB ±0.8 dB | -11.8dB ±0.7 dB |