Visible to Intel only — GUID: bkk1683210374349

Ixiasoft

Visible to Intel only — GUID: bkk1683210374349

Ixiasoft

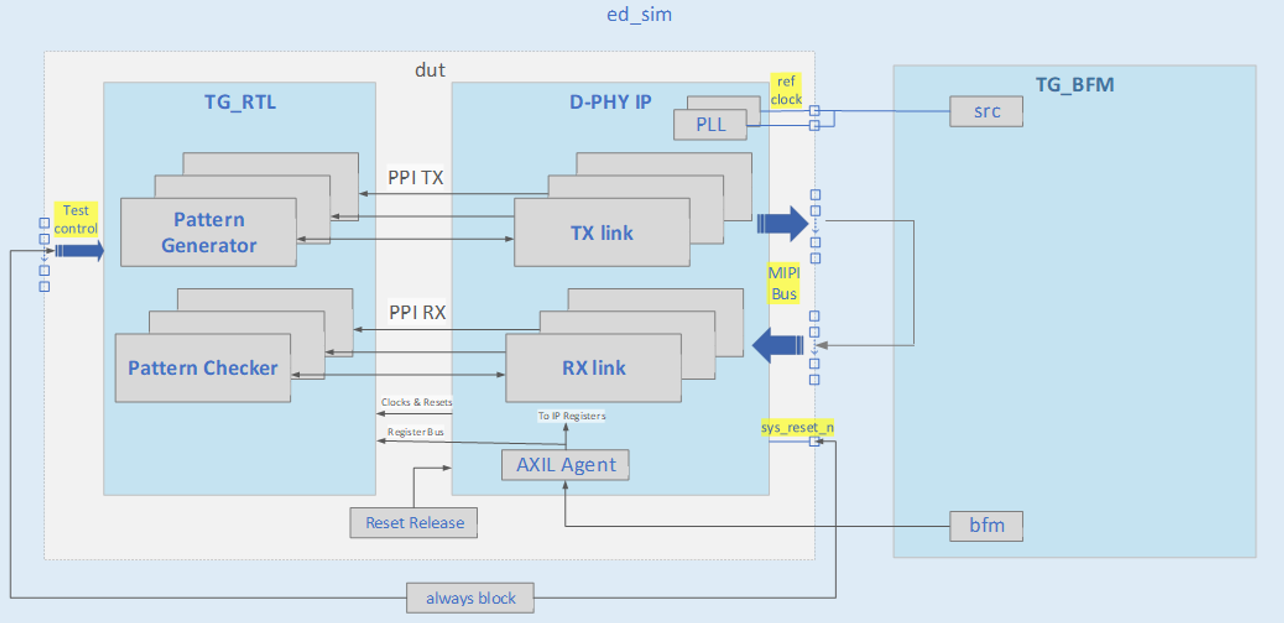

5.5.2.1. Simulation Design Example with External Loopback Enabled Block Diagram

Alternatively, you could instantiate two IPs for TX and RX, respectively. When TX and RX links are instantiated within the same IP, the D-PHY IP checks for the RX-TX pairing for loopback and passes that information to the TG_BFM block for enabling the loopbacks among the different links.

The simulation design example with external loopback enabled contains the major blocks shown in the figure below:

As described in the previous section, the synthesis design example contains a traffic generator and an instance of the D-PHY IP.

The TG_BFM model, which includes the following functions:

- Clock source for PLL reference clock.

- AXI-Lite interface instantiation which contains read/write tasks and can be used as an AXI-Lite BFM.

- Loopback MUXing for looping back TX links to RX links on the same D-PHY IP.