Visible to Intel only — GUID: gtk1682532919431

Ixiasoft

1. About the External Memory Interfaces Agilex™ 5 FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Agilex™ 5 FPGA IP

3. Design Example Description for External Memory Interfaces Agilex™ 5 FPGA IP

4. Document Revision History for External Memory Interfaces (EMIF) IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Configuring DQ Pin Swizzling

2.4. Generating the Synthesizable EMIF Design Example

2.5. Generating the EMIF Design Example for Simulation

2.6. Pin Placement for Agilex™ 5 EMIF IP

2.7. Compiling the Agilex™ 5 EMIF Design Example

2.8. Using the Design Example with the Test Engine IP

2.9. Generating the EMIF Design Example with the Performance Monitor

2.3.1. Example: DQ Pin Swizzling Within DQS Group for x32+ECC DDR4 Interface

2.3.2. Example: Byte Swizzling for x32 DDR4 Interface, Using a Memory Device of x8 Width

2.3.3. Combining Pin and Byte Swizzling

2.3.4. Example: Swizzling for x32 + ECC DDR4 Interface

2.3.5. Example: Byte Swizzling for Lockstep Configuration

Visible to Intel only — GUID: gtk1682532919431

Ixiasoft

2.1.1.3.1. Generating a Custom Memory Preset File for DDR4

To generate a custom preset file for DDR4, follow these steps:

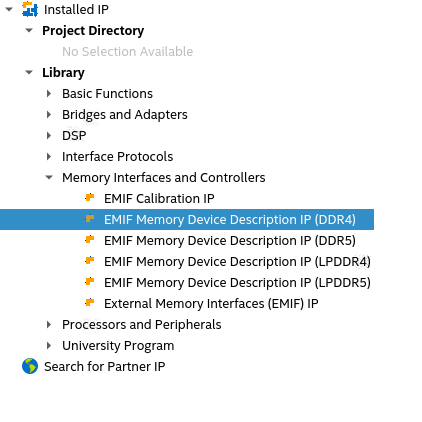

- In the IP Catalog window, select Memory Device Description IP (DDR4).

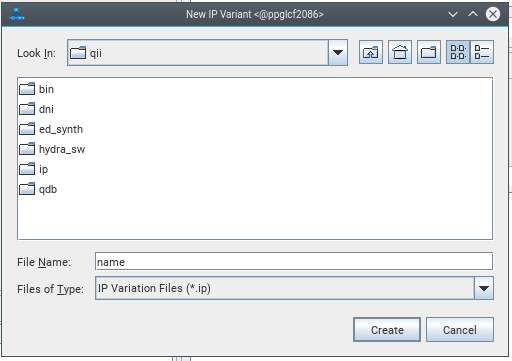

- Type the name for the IP instance and click Create.

- Refer to the images below for the steps in creating and saving the custom presets file:

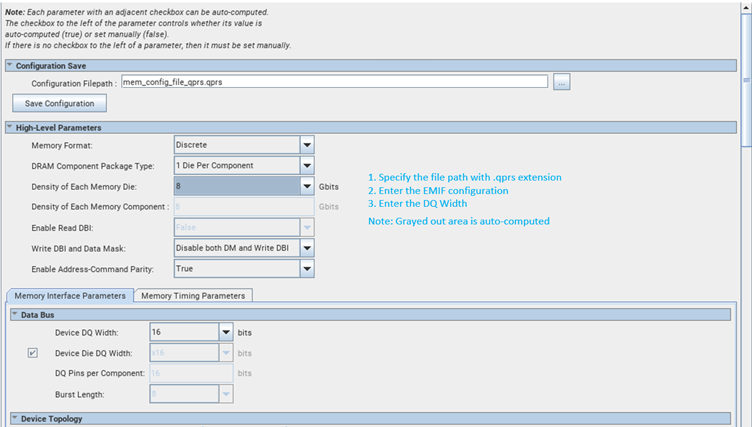

Figure 8. Parameterizing EMIF Memory Device Description IP (DDR4) – Part 1

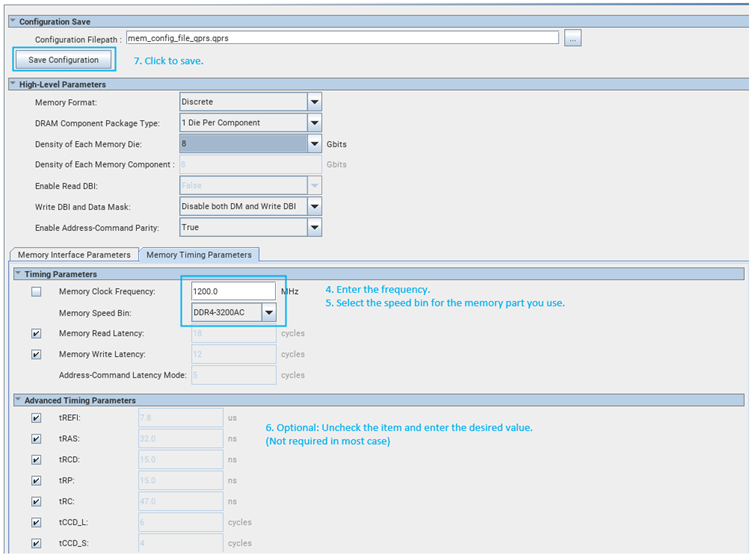

Figure 9. Parameterizing EMIF Memory Device Description IP (DDR4) – Part 2

Figure 9. Parameterizing EMIF Memory Device Description IP (DDR4) – Part 2