Visible to Intel only — GUID: inq1717003218814

Ixiasoft

Visible to Intel only — GUID: inq1717003218814

Ixiasoft

2.3.2. Example: Byte Swizzling for x32 DDR4 Interface, Using a Memory Device of x8 Width

| Lane Number | BL0 | BL1 | BL2 | BL3 | BL4 | BL5 | BL6 | BL7 |

|---|---|---|---|---|---|---|---|---|

| Default Placement | DQ[0] | AC[0] | AC[1] | AC[2] | DQ[1] | DQ[2] | DQ[3] | GPIO |

| After Byte Swizzling | DQ[2] | AC[0] | AC[1] | AC[2] | DQ[1] | DQ[0] | DQ[3] | GPIO |

| BYTE SWIZZLE | 2 | X | X | X | 1 | 0 | 3 | X |

This example illustrates swizzling DQS group 0 with DQS group 2. The BYTE_SWIZZLE_CH0 denotes the DQS group implemented in the lane after the swizzling. X indicates that the lane is not used as a data lane (meaning that it serves as an address/command lane or is not used by the EMIF interface).

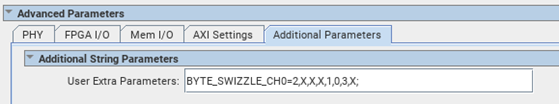

To achieve this swizzling, you must enter BYTE_SWIZZLE_CH0=2,X,X,X,1,0,3,X; in the User Extra Parameters field of the Additional Parameters tab in the Advanced Parameters section of the General IP Parameters tab in the External Memory Interfaces IP parameter editor.