Visible to Intel only — GUID: kyf1682532819661

Ixiasoft

1. About the External Memory Interfaces Agilex™ 5 FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Agilex™ 5 FPGA IP

3. Design Example Description for External Memory Interfaces Agilex™ 5 FPGA IP

4. Document Revision History for External Memory Interfaces (EMIF) IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Configuring DQ Pin Swizzling

2.4. Generating the Synthesizable EMIF Design Example

2.5. Generating the EMIF Design Example for Simulation

2.6. Pin Placement for Agilex™ 5 EMIF IP

2.7. Compiling the Agilex™ 5 EMIF Design Example

2.8. Using the Design Example with the Test Engine IP

2.9. Generating the EMIF Design Example with the Performance Monitor

2.3.1. Example: DQ Pin Swizzling Within DQS Group for x32+ECC DDR4 Interface

2.3.2. Example: Byte Swizzling for x32 DDR4 Interface, Using a Memory Device of x8 Width

2.3.3. Combining Pin and Byte Swizzling

2.3.4. Example: Swizzling for x32 + ECC DDR4 Interface

2.3.5. Example: Byte Swizzling for Lockstep Configuration

Visible to Intel only — GUID: kyf1682532819661

Ixiasoft

2.1. Creating an EMIF Project

You must create an Quartus® Prime project before generating the Agilex™ 5 EMIF IP and design example.

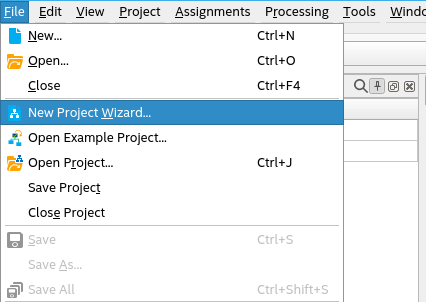

- Launch the Quartus® Prime software and select File > New Project Wizard. Click Next.

Figure 2. File Menu

- Specify a directory (<user project directory>), a name for the Quartus® Prime project (<user project name>), and a top-level design entity name (<user top-level instance name>) that you want to create.

- Verify that Empty Project is selected.

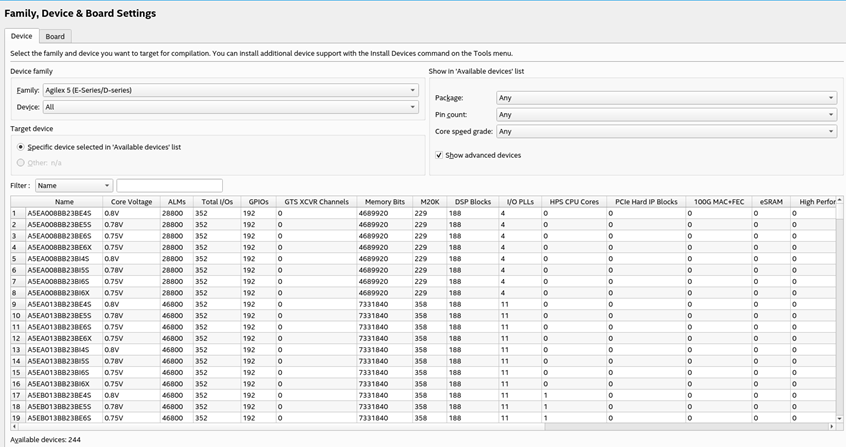

- Under Family, select Agilex™ 5 (E-Series).

- Under Name filter, type the device part number.

- Under Available devices, select the appropriate device.

Figure 3. Family, Device, and Board Settings

- Click Finish.