Visible to Intel only — GUID: ove1613681232880

Ixiasoft

5.1. Clock Signals

5.2. Reset Signals

5.3. TX MII Interface (64b/66b)

5.4. RX MII Interface (64b/66b)

5.5. Status Interface for 64b/66b Line Rate

5.6. TX Interface (8b/10b)

5.7. RX Interface (8b/10b)

5.8. Status Interface for 8b/10b Line Rate

5.9. Serial Interface

5.10. CPRI PHY Reconfiguration Interface

5.11. Datapath Avalon Memory-Mapped Interface

5.12. PMA Avalon Memory-Mapped Interface

Visible to Intel only — GUID: ove1613681232880

Ixiasoft

5.10. CPRI PHY Reconfiguration Interface

| Port Name | Width (Bits) | Domain | Description |

|---|---|---|---|

| i_reconfig_cpri_addr[3:0] | 4 | i_reconfig_clk | Address for F-tile CPRI PHY CSRs in the selected channel. Using word addressing format. |

| i_reconfig_cpri_read | 1 | i_reconfig_clk | Read command for F-tile CPRI PHY CSRs in the selected channel. |

| i_reconfig_cpri_write | 1 | i_reconfig_clk | Write command for F-tile CPRI PHY CSRs in the selected channel. |

| o_reconfig_cpri_readdata[31:0] | 32 | i_reconfig_clk | Read data from reads to F-tile CPRI PHY CSRs in the selected channel. |

| o_reconfig_cpri_readdatavalid | 1 | i_reconfig_clk | Read data from F-tile CPRI PHY CSRs is valid in the selected channel. |

| i_reconfig_cpri_writedata[31:0] | 32 | i_reconfig_clk | Data for writes to F-tile CPRI PHY CSRs in the selected channel. |

| o_reconfig_cpri_waitrequest | 1 | i_reconfig_clk | Avalon® memory-mapped interface stalling signal for operations on F-tile CPRI PHY CSRs in the selected channel. |

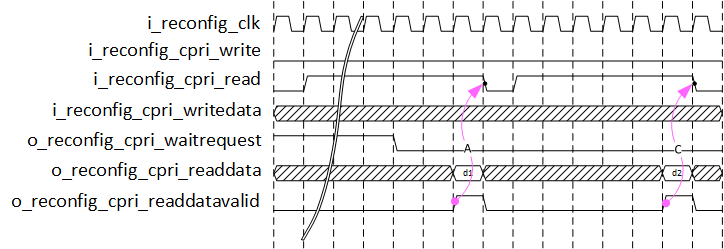

Figure 10. Writing to CPRI PHY Reconfiguration

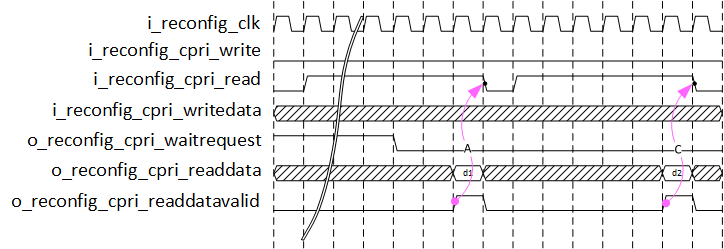

Figure 11. Reading from CPRI PHY Reconfiguration