AN 766: Intel® Stratix® 10 Devices, High Speed Signal Interface Layout Design Guideline

Visible to Intel only — GUID: joc1463335304047

Ixiasoft

Visible to Intel only — GUID: joc1463335304047

Ixiasoft

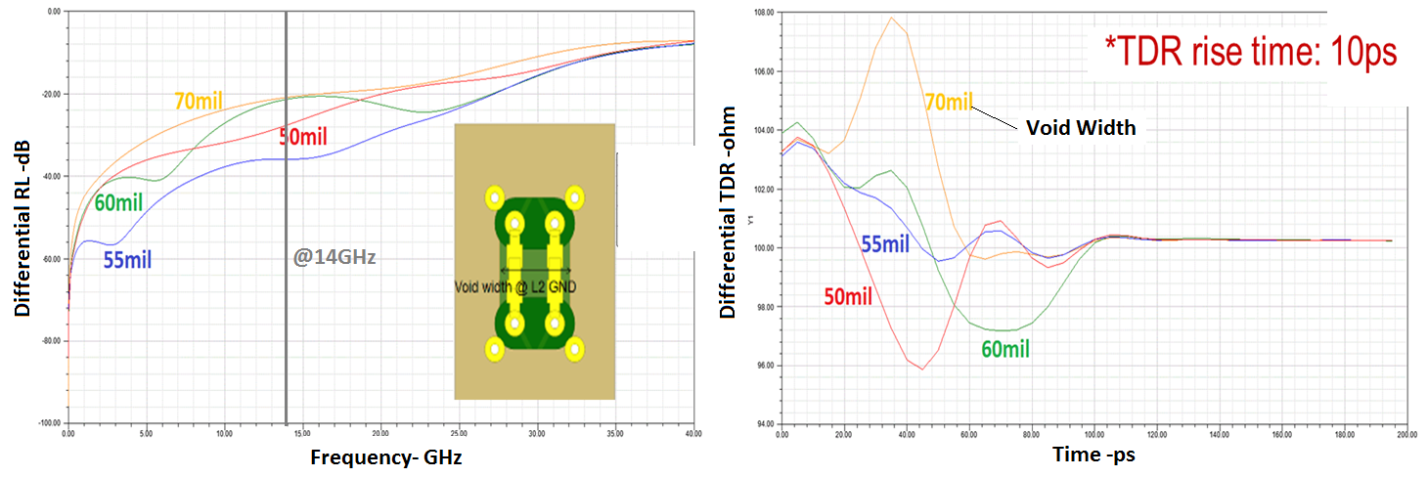

Sweeping Void Width only on the First GND Plane Under the Capacitor

Keeping the via anti-pad radius fixed while adjusting the void width on the first GND plane under the AC capacitors also impacts the structure's impedance.

Changing the void width from 50 mil to 70 mil impacts the structure's impedance and return loss. A 55 mil void width is the optimum solution for this case and results in the least mismatching.