Visible to Intel only — GUID: joc1463371796875

Ixiasoft

Visible to Intel only — GUID: joc1463371796875

Ixiasoft

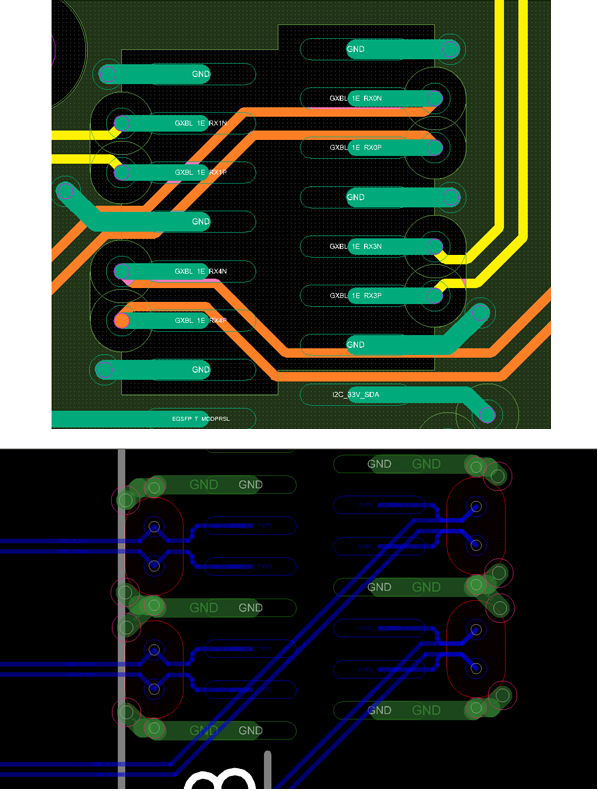

Recommended QSFP+ Signal Routing

You must ensure that you have a proper GND reference plane for signal routing. The differential lanes in yellow can be routed on any signal layer. The differential lanes in orange can only be routed on any signal layer in which the GND reference layers are not GND02/GND04. This is due to crossing the cutout area below the connector.

The orange differential lanes can be routed from the opposite direction (similar to the yellow lanes) provided that there is adequate space for routing. In this case, all signal layers can be used for signal routing.

Observe these guidelines for improved QSFP+ performance at 28 Gbps on the main channel:

- Length matching for each pair (between P and N lanes) is required. Both P and N lanes must be in phase to recover the data. The skew matching in a pair is 2 ps.

- Length matching between pairs is not required unless specified by a designer.

- For optimized FPGA break-out layout design, refer to FPGA Fan-out Region chapter.

- Always use the minimum routing length from the FPGA to the connector to minimize insertion loss. Refer to PCS Stackup Selection Guideline chapter for stack-up and material selection, and Recommendations for High Speed Signal PCB Routing chapter for HSSI PCB routing.

- The insertion and return loss of the channel must meet specifications. Refer to Electrical Specifications chapter.