Visible to Intel only — GUID: joc1463592498768

Ixiasoft

Visible to Intel only — GUID: joc1463592498768

Ixiasoft

Interlaken Channel Interface Performance Example

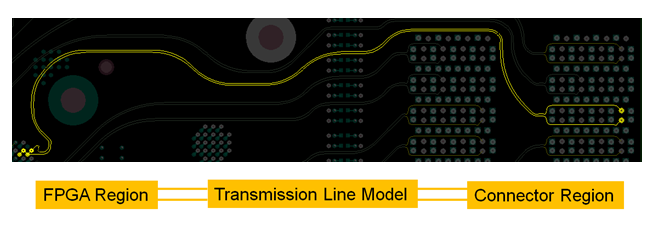

The channel in this example is designed for the Interlaken interface using a TYCO Interlaken connector. The board layout recommendations provided above are used in this channel design. This example design is implemented on the Intel® Arria® 10 device development kit.

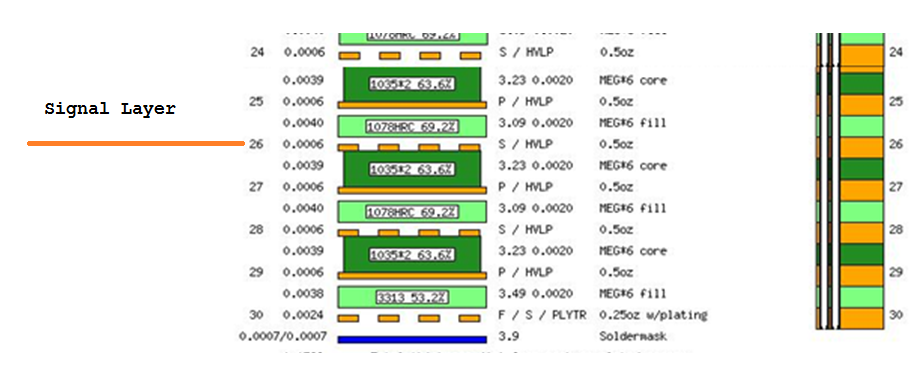

A TX channel has been selected for these 3D HFSS simulations. The TX channel is routed on layer 26 using a back-drill up to layer 27. The total PCB routing is approximately 3.94 inch using stripline routing with rounded corners.

- 30 layers

- Copper Foil - HVLP

- Surface roughness = 2 µm

- Back-drill

- Material = Megtron6

- Total thickness = 153.3 mil

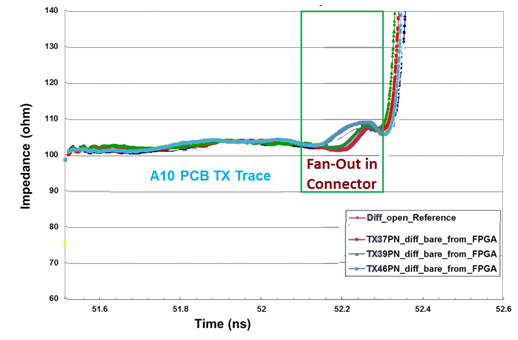

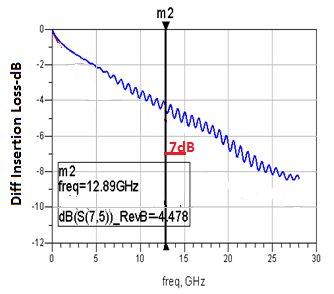

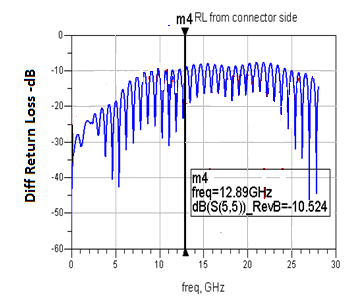

The following figures show the host PCB TX channel performance from the FPGA BGA/ball to the Interlaken connector signal pads on the top layer.

The insertion loss is below the mentioned specifications in Electrical Specifications chapter, which specifies less than 7 dB insertion loss for the host PCB.