Visible to Intel only — GUID: joc1462997219312

Ixiasoft

Visible to Intel only — GUID: joc1462997219312

Ixiasoft

Signal Break-out Recommendations

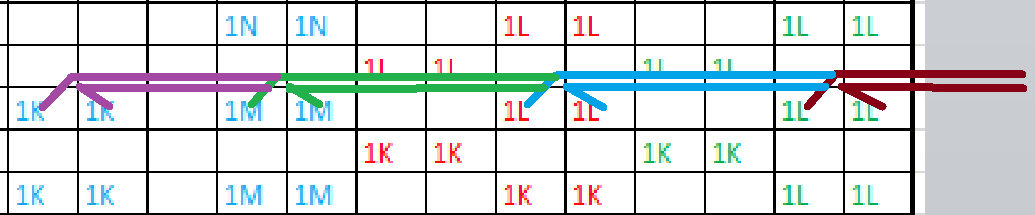

Figure Figure 3 shows that there are up to 4 transceiver pairs in one row for Intel® Stratix® 10 devices. Designers must assign at least 4 signals layers each separated by continuous ground planes for break-out routing. The number of layers assigned for transceivers routing is one of the key factors for stackup selection. Intel recommends that you follow FPGA break-out region guideline in the next section to achieve optimum performance.

There are three options for FPGA fan-out region routing. Each one can be selected for high speed signal routing on PCB, based on their high priority and data rate.

- Option 1: Via-In-Pad Topology

- Option 2: Dog-bone with GND Cutout at BGA Pad Topology

- Option 3: Micro-via Topology

- GND Cutout Under BGA Pads in Fan-out Configuration

- Comparison of Dog-bone with GND Cutout Under the BGA and Via-in-Pad Configurations

- Trace Shape Routing at the BGA Void Area (Tear Drop Configuration)