AN 766: Intel® Stratix® 10 Devices, High Speed Signal Interface Layout Design Guideline

Visible to Intel only — GUID: joc1463351654778

Ixiasoft

Visible to Intel only — GUID: joc1463351654778

Ixiasoft

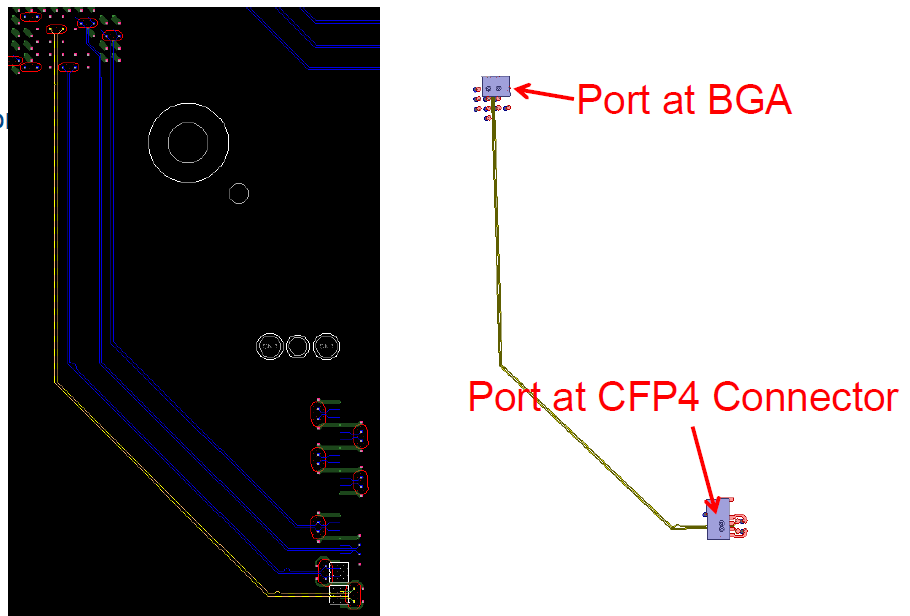

Full CFP4 Channel Analysis Design Example (Excluding the Connector)

This section illustrates a full FP4 channel simulation.

The total channel length is approximately 2.4 inch from the BGA to the connector pads.

The main routing is stripline on layer 5. The connector break-out configuration is similar to what you can see at pair 2 in .

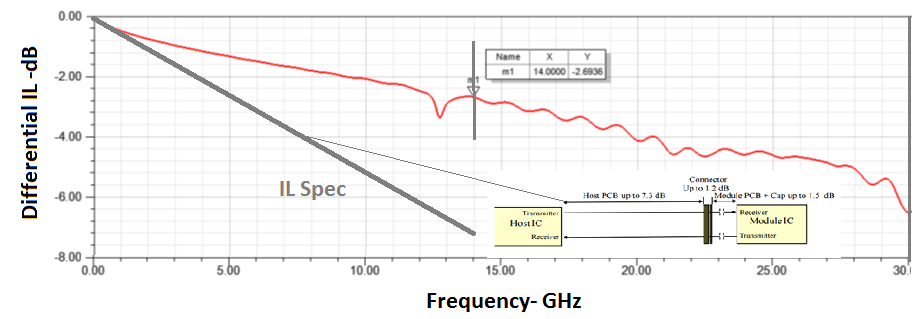

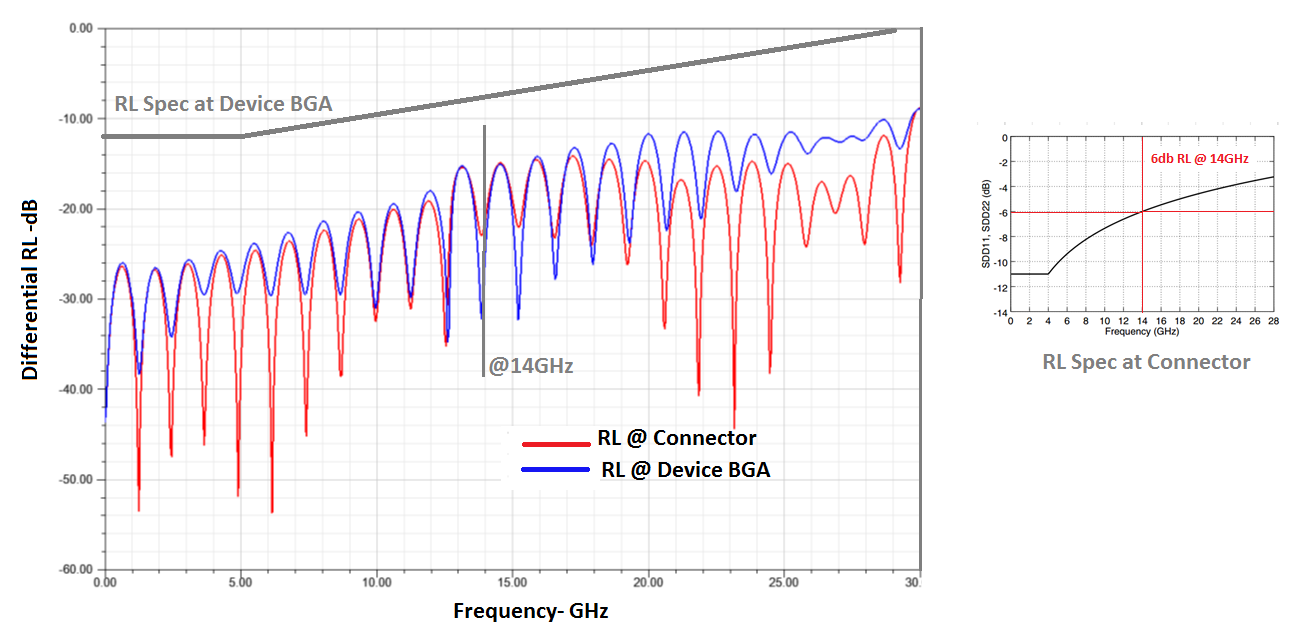

Comparing the scattering performances (SDD21 and SDD11/22) above with the host-to-module specification in CEI-28G-VSR shows that both insertion and return loss meet the specifications.