Visible to Intel only — GUID: joc1463352508732

Ixiasoft

Visible to Intel only — GUID: joc1463352508732

Ixiasoft

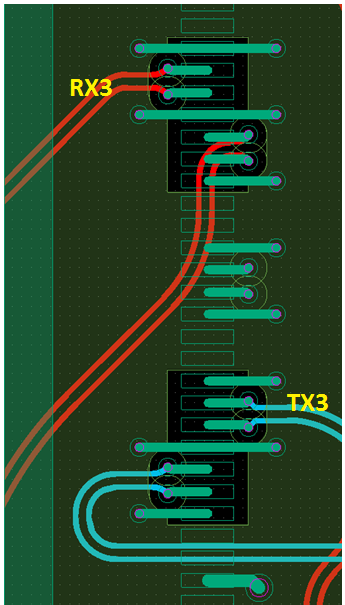

CFP2 Connector Area Layout

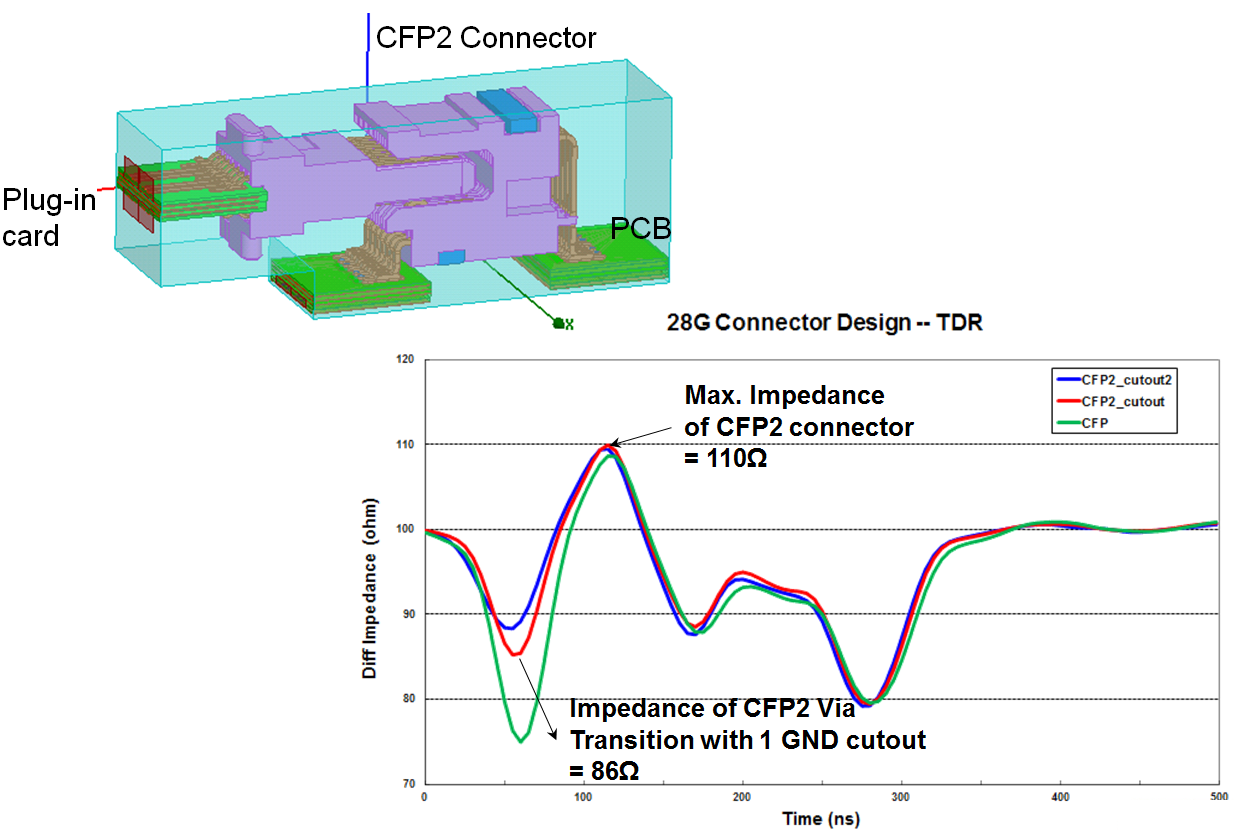

These are the differential TDR results from simulation including the PCB portion connected to the CFP2 connector and host compliance board. The TDR result is based on the following configuration:

- No GND cutout

- One single GND layer cutout

- Two GND layer cutouts below the CFP2 high speed signal pads

The host PCB routing has a 100 Ω impedance.

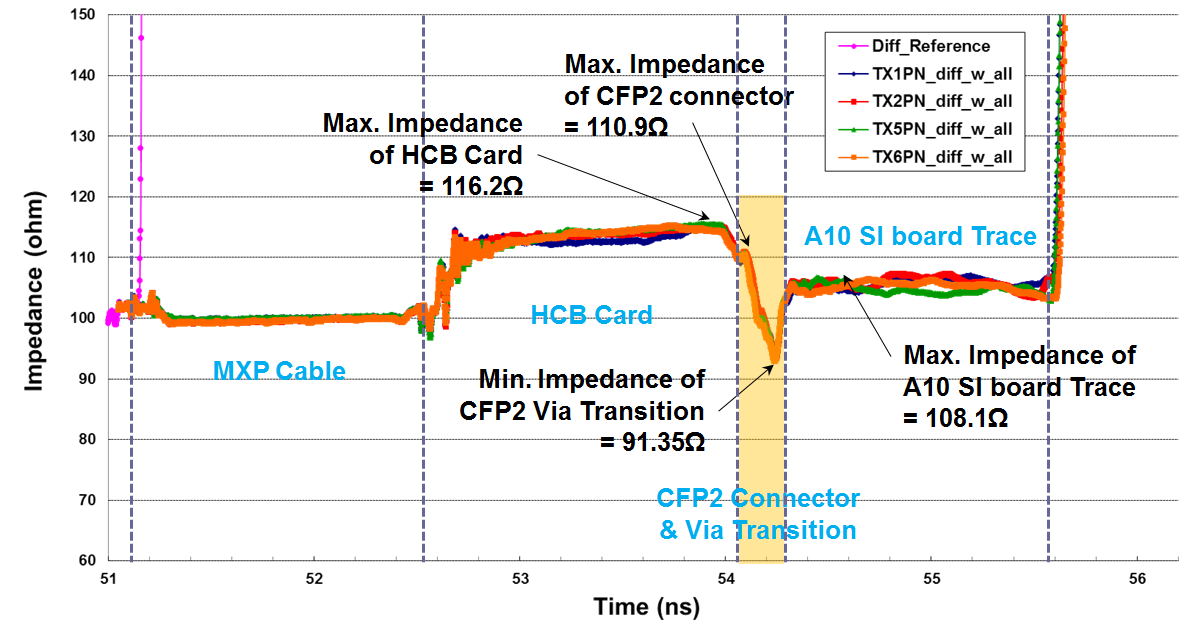

The following figure shows the actual measured differential TDR on an Intel® Arria® 10 device populated SI board for CFP2 full channel. Two GND layers are cut out below the high speed connector pads. The reduced differential impedance is approximately 8.5 Ω at the CFP2 connector transition to the PCB.

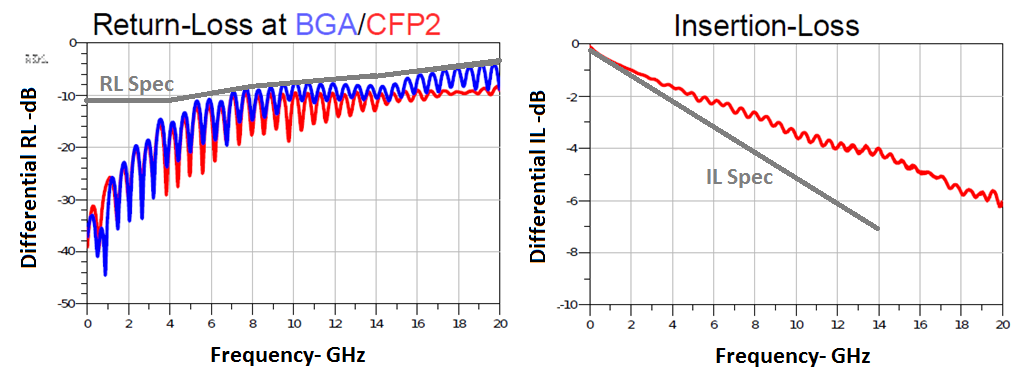

Measured SP performances for one single TX pair and one single RX pair which both meet the CFP2 specification.